광주과학기술원(GIST)은 전기전자컴퓨터공학과 홍성민 교수 연구팀이 반도체 소자 시뮬레이션의 계산 효율을 혁신적으로 개선해, 기존 대비 최대 100배 빠른 속도로 차세대 소자의 성능을 예측할 수 있는 새로운 알고리즘을 개발했다고 밝혔다. 이번 성과는 반도체 소자 연구개발(R&D) 과정에서 가장 큰 걸림돌로 꼽히던 ‘장시간 시뮬레이션’ 문제를 근본적으로 해결했다는 점에서 의미가 크다.

반도체 소자 시뮬레이션(Semiconductor Device Simulation)은 반도체의 전기적·물리적 동작을 가상 환경에서 수치적으로 재현하고 분석하는 기술이다. 전류의 흐름, 전계 분포, 발열 특성 등 소자의 거동을 실제 제작 이전에 예측할 수 있어 성능 최적화와 설계 효율성을 높이는 핵심 도구로, TCAD(Technology Computer-Aided Design) 분야에서 폭넓게 활용된다.

차세대 반도체 소자의 성능을 사전에 예측하고 최적화하기 위해 필수적인 TCAD 시뮬레이션은 반도체 내부에서 전자와 정공의 이동, 전기장 분포 등을 물리 법칙에 따라 계산해 전기적 특성을 정밀하게 예측한다. 그러나 게이트올어라운드(GAA) 구조나 보완형 트랜지스터(CFET) 등 복잡한 3차원 구조에서는 계산이 방대해 수 시간에서 수 일이 소요되는 경우가 많아 연구개발 속도가 크게 늦어지는 한계가 있었다.

특히 원하는 전압 조건에서 안정적인 계산을 위해 전압을 점진적으로 높이며 수렴을 유도하는 ‘바이어스 램핑(bias-ramping)’ 과정이 필수적이었는데, 이 과정이 전체 계산 시간의 대부분을 차지해 병목으로 작용했다. 이를 보완하기 위해 인공지능(AI) 기반 인공신경망(ANN) 모델을 이용해 초기 추정값을 생성하는 연구도 있었지만, 새로운 소자 구조에 적용하려면 추가 학습이 필요해 즉각적인 산업 현장 적용에는 제약이 있었다.

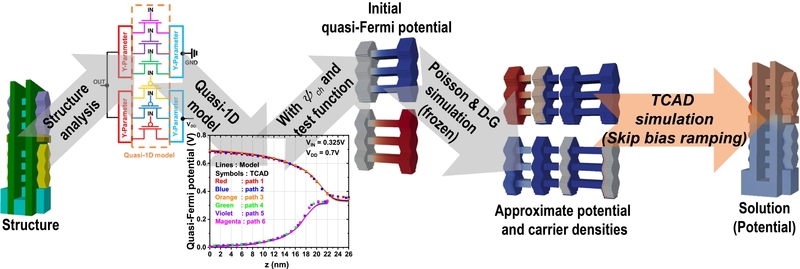

홍성민 교수 연구팀은 이러한 문제를 해결하기 위해 ‘준(準) 1차원(Quasi-1D) 모델링’과 ‘영역별 구조 분석(Region-wise Structure Analysis)’을 결합한 새로운 접근법을 제안했다. 이 방법은 사전 학습 과정 없이도 시뮬레이션 수행 시간을 획기적으로 단축할 수 있다.

핵심은 복잡한 반도체 구조를 전류가 흐르는 채널 방향에 따라 1차원으로 단순화해 빠르게 초기 계산값(solution)을 추정하고, 소자를 여러 구간으로 나눠 각 구간에 최적화된 물리 모델을 적용하는 것이다. 이를 통해 기존에 필수적이던 바이어스 램핑 과정을 생략하면서도 10~100배 빠른 계산 속도를 구현했다.

연구팀은 게이트올어라운드(GAA) 소자, 보완형 트랜지스터(CFET) 인버터 등 다양한 차세대 소자에 해당 알고리즘을 적용해 검증했다. 그 결과, 시뮬레이션 속도는 기존 대비 10~100배 이상 빨라졌으며, 전압 전달 특성(VTC) 등 주요 전기적 특성에서도 기존 TCAD 결과와의 오차가 0.1볼트(V) 이하로 억제돼 높은 정확성을 입증했다. 또한 소자의 형태나 계산 과정에서 나누는 메쉬(mesh) 조건이 달라져도 일관된 결과를 보여, 다양한 환경에서도 안정적으로 적용할 수 있음을 확인했다.

홍 교수는 “이번 연구는 사전 학습된 인공신경망 기반 AI 모델이 없어도 다양한 구조에서 반도체 소자 시뮬레이션 시간을 대폭 단축할 수 있음을 보여준 성과”라며 “효율성과 정확성, 안정성을 모두 갖춘 이번 기법이 차세대 반도체 소자 개발 속도를 높이고 연구 효율을 극대화하는 데 기여할 것”이라고 말했다.

이번 연구는 GIST 전기전자컴퓨터공학과 홍성민 교수의 지도 아래 이광운, 김인기, 정승우, 장민서 연구원이 참여했으며, 과학기술정보통신부·한국연구재단 개인기초연구사업(중견)의 지원을 받았다. 연구 결과는 국제학술지 ‘커뮤니케이션스 엔지니어링’(Communications Engineering)에 2025년 9월 25일 온라인 게재됐다.

헬로티 이창현 기자 |