헬로티 서재창 기자 |

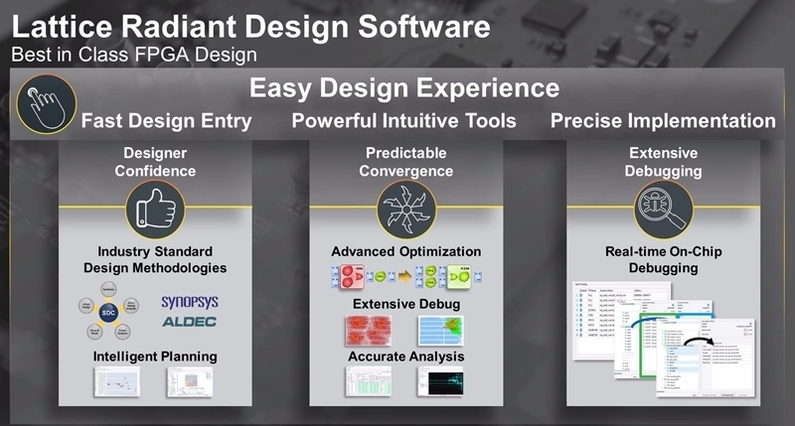

래티스 반도체(이하 래티스)는 오늘 온라인으로 개최된 신제품 발표회를 통해 자사의 저전력 FPGA와 함께 사용하는 소프트웨어 설계 툴의 최신 버전 'Lattice Radiant 3.0'을 발표했다.

이 툴은 래티스 넥서스 플랫폼을 기반으로 하는 최신 제품군인 새로운 래티스 CertusPro-NX 제품군 같이 높은 밀도의 디바이스를 지원하며, 래티스 FPGA를 기반으로 하는 시스템 설계를 손쉽게 개발하는 새로운 기능을 제공한다.

시스템 개발자가 하드웨어 플랫폼을 평가할 때 실제 하드웨어는 여러 선택 기준 중 하나일 뿐이다. 개발자는 하드웨어와 함께 해당 하드웨어를 설정하는 데 사용되는 설계 소프트웨어 또한 사용 편의성과 지원 기능을 중심으로 평가하는데, 그 이유는 이러한 특성이 전반적인 시스템 개발 시간과 비용에 상당한 영향을 미치기 때문이다.

안티 루카츠(Antti Lukats) 트렌즈 일렉트로닉스 CTO는 “산업 및 자동차 시장을 위한 FPGA 기반 SoM(system on module) 솔루션의 선도 기업으로서, 우리는 수십 년 동안 하드웨어 개발에 사용되는 다양한 소프트웨어 툴을 경험해봤다”고 밝혔다.

안티 루카츠 CTO는 “Lattice Radiant 툴은 매우 직관적이고 사용하기 쉬운 최신 사용자 인터페이스로 설계 복잡성을 줄이고 제품을 빠르게 출시되도록 해준다"고 말했다.

래티스 반도체의 소프트웨어 제품 라인을 담당하는 로저 도(Roger Do) 선임 매니저는 “Lattice Radiant 3.0 설계 소프트웨어는 개발자가 손쉽게 따라하는 사용자 경험을 제공한다. 이 툴은 개발자에게 설계 생성, IP 가져오기, 구현, 비트 스트림 생성, FPGA로 비트 스트림 다운로드, 디버깅 등 일련의 개발 흐름을 단계별로 안내한다”고 말했다.

이어 그는 “FPGA 작업 경험이 거의 또는 전혀 없는 개발자라면 Lattice Radiant의 자동화된 기능을 빠르게 활용하고, 숙련된 FPGA 개발자는 Lattice Radiant 3.0을 사용해 특정 최적화가 필요한 경우 FPGA 설정을 보다 세밀하게 제어할 수 있다”고 덧붙였다.

Radiant 3.0에서 새롭게 업그레이드된 기능은 다음과 같다.

Radiant 3.0의 SERDES 분석 툴은 CertusPro-NX 디바이스가 지원하는 보다 높은 SERDES 대역폭을 수용할 수 있게 향상됐다. 그래픽 사용자 인터페이스를 통해 설계 흐름 전반에 걸쳐 신호 추적 기능이 향상돼 설계자는 HDL 소스에서 RTL보기, 기술 보기로, 그리고 다시 되돌아오는 과정에서 신호를 추적한다.

Radiant를 활용하면, 사용자가 LSE(Lattice Synthesis Engine)와 Synplify Pro 합성 엔진 중에서 원하는 엔진을 선택할 수 있다. Radiant 3.0에서는 타이밍 제한과 타이밍 분석이 이들 두 합성 엔진에 통합됐다.

Radiant 3.0에서는 타이밍 분석이 다른 작업과 분리돼 있으므로 독립적으로 실행할 수 있다. 이는 설계자가 매핑과 배치 및 경로 지정을 재실행하지 않고도 'what-if' 시나리오를 평가하고 타이밍 분석을 다시 실행할 수 있게 함으로써 반복적인 설계 프로세스의 속도를 극적으로 향상시킨다.

이전 배포판과 비교할 때, Radiant 3.0은 평균적으로 런타임은 15% 짧아지고, 설계 성능은 7% 향상됐다.