우주비행용FPGA인RTAX-DSP에서

SEE를저감하는방법

IC 기판에 고에너지 이온이 스페이스 스트라이크로 나타나면 IC 회로에 순간적인 전류/전압 펄스를 일으킬 수 있다. 이 펄스가 회로상의 데이터를 변경시킬 정도로 클 때 우리는 이러한 펄스를 총칭하여 SEE(Single-Event Effect)라고 한다. SEE에 대한 두 가지 하위 분류는 실제 RTAX-DSP 설계자가 큰 관심을 갖고 있는 부분이다.

Sana Rezgui 마이크로세미 기술팀

SEE에 대한 2가지 분류

1. SEU(Single-Event Upset)

SEU는 아마 SEE에 대해 가장 이해 도가 높은 분류로 규정할 수 있을 것이 다. SEU는 충분한 전하가 정적 메모리 요소(래치, 레지스터 또는 SRAM 셀)에 모일 때, 전압은 상태를 변경시킬 수 있 는 정적 메모리 요소를 야기시킨다. 이 러한 오류나 업셋은 새로운 데이터가 메모리 요소에 기록되는 다음 순서까지 남게 된다.

2. SET(Single-Event Transient)

영향을 미치는 이온이 하나의 디바이 스 내 혼합형 회로에서 전압 펄스를 유 도할 때 이러한 효과는 SET라고 알려 져 있다. 유도 전압 레벨이 스위칭 임계값 수 준을 초과하고 펄스 폭이 충분하다면 오류성 데이터의 값은 회로 전체로 전 파된다. 명칭에서 암시하듯이, 이러한 오류는 500ps의 순차에서 펄스 폭으로 자연스럽게 일시적이 된다.

저감 방법

디지털 로직에서 SEE에 대응하는 데 에는 수많은 저감 방법이 존재한다. SRAM 블록에서의 SEU 효과는 메모리 에서 EDAC(Error Detection and Correction) 회로를 사용함으로써 저감 할 수 있다. 일반적으로 ECC(Error- Correcting Code) 방식이다. 여기서 리 던던트 메모리 비트는 사용자 데이터와 동시에 저장되며 메모리에 대한 어떠한 오류나 업셋을 감지하여 수정하는 것을 돕는다. 구현되는 ECC의 유형에 따라 주어진 데이터 단어에 의한 싱글 및 더 블 비트 오류를 감지할 수 있다. EDAC 솔루션은 쉽게 이용할 수 있으며 설계 자들이 쉽게 구현할 수 있다.

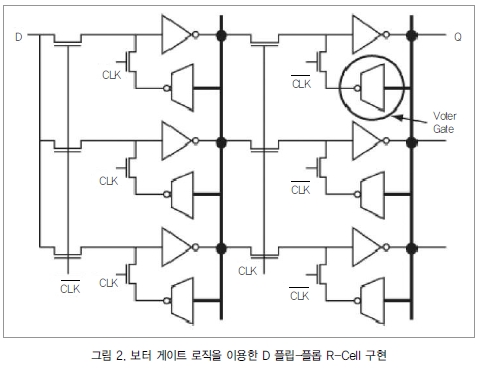

레지스터 요소에 있어서 저감 오류는 SRAM의 블록에 비해 덜 간단하다. SEE가 국한되므로 영향을 미치는 이온 은 단일 p-n 접합에만 영향을 줄 수 있 으며, 병렬 회로는 레지스터 SEU를 모으기 위해 구동될 수 있다. 가장 일반적 으로 사용되는 방법은 TMR(Triple Module Redundancy)이라고 하는 리 던던시 형태이다. TMR에서 3가지의 레지스터(플립-플롭)는 병렬로 사용되 며, 그 결과 과반수 투표제 회로를 갖추 게 된다. SEU가 플립 플롭에서 발생될 경우, 다른 두 개는 여전히 정확한 데이 터를 지나가는 보팅 회로(Voting Circuit)의 정확한 데이터를 포함하게 된다. SET 정정은 오류의 과도 속성 때 문에 더욱 복잡해 진다. 관련 회로와 지 연되는 톨러런스에 따라 두 가지 방법 이 사용될 수 있다. 트리플 드라이브 (Tripe-Drive)로 언급되는 저감 기법에 서, 래치의 출력 버퍼는 3배로 된다. 3 배화된 버퍼 중 하나가 SET를 겪는다 면, 다른 2개는 이벤트를 진압하고 정확 한 신호를 유지시킬 것이다.

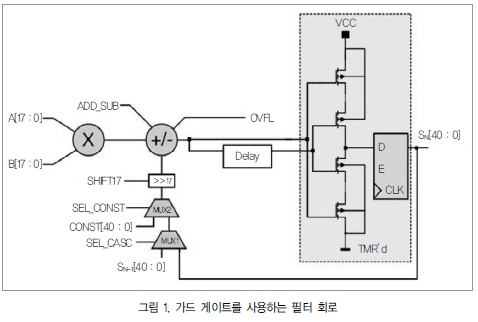

SET 저감 방법의 두 번째 유형은 가 드 게이트를 이용한 필터 회로를 사용 하는 것이다. 이 필터는 두 가지 경로에 대한 원래의 신호 경로를 분산시킨다. 가드 게이트로 직접 가는 경로와, 원래 신호에 지연을 유발시키는 인버터 스트 링을 통해서이다. 가드 게이트는 AND 게이트로 기능한다. 이 때 2개의 입력이 동의되거나 입력 신호가 다를 경우, 이 전 상태의 래치가 인버터 스트링 지연 보다 펄스 폭으로 과도 상태를 필터링 시킨다.

RTAX-DSP vs. RTAX-S/SL

RTAX-DSP 디바이스는 RTAXS/ SL FPGA에 사용하는 동일한 0.15㎛ CMOS 공정을 사용하여 제조되며 동일 한 베이스 패브릭을 공유한다. 마이크 로세미의 래디에이션 톨러런트 (Radiation-Tolerant) FPGA 최근 제 품군의 경우, 임베디드 래디에이션 톨 러런트 멀티플라이 어큐뮬레이트 블록 (DSP Mathblock)이 성공적으로 RTAX-S 회로에 추가됐다. 이 새로운 제품군은 DSP 기능성 외에도 SEU 보 호형 플립플롭 설계에 대한 변경 기능 이 있어, RTAX-S/SL이 제공하는 높은 수준에서 FPGA 패브릭의 SEE 성능을 더욱 향상시킨다.

RTAX-S R-Cell 저감 및 RTAX-DSP 향상

RTAX 아키텍처는 FPGA 코어에서 R-Cell과 C-Cell의 두 가지 로직 유형 을 갖는다. C-Cell은 산술 기능을 구현 하는 데 캐리 연산으로 최대 5개 입력을 통해 4,000개 이상의 통합 기능을 구현 할 수 있다. R-Cell은 단일 D-타입의 플립플롭을 구현하여 비동기식 클리어, 비동기식 프리셋, 액티브 로우 이네이 블 제어 신호와 함께 프로그램 가능한 클록 극성을 갖고 있다.

SEU에 있어서 R-Cell을 강화하기 위해, 래치는 TMR을 이용하여 구현된 다. 각각의 RTAX R-Cell은 세 가지 마 스터 슬레이브 래치 페어를 이용하여 구성됐으며, 각각 비동기식 셀프-수정 용 피드백 경로를 갖추고 있다.

마스터나 슬레이브 측면에서의 각 래 치에 대한 출력은 다른 측면에서 다른 2 개의 래치 출력을 선출한다. 3개의 래치 중 하나가 이온에 의해 타격 받아 상태 를 변경시키기 시작했다면, 다른 2개의 래치로 선출할 경우 변경이 후행하는 것과 영구적으로 래칭하는 것을 막아준 다. 한 번의 이온 충격이 하나 이상의 래 치에 영향을 줄 수 없도록 하기 위해 레 이아웃에서도 보호를 받는다. 더욱 추 가적인 세부사항을 알고 싶다면 RTAXS/SL RadTolerant FPGA 데이 터시트를 참조한다.

RTAX-S R-Cell이 SEU에 대해 견 고해진다고 해도 SET에는 여전히 민감 할 수 있다. 마이크로세미가 실시하는 빔 테스트는 Aerospace Corporation의 래디에이션 그룹에서 검증했으며, 대부분의 RTAX-S/SL FPGA SET 오 류가 R-Cell에서 이온 스트라이크에 의 해 기원된다는 것을 나타낸다. 상세한 분석은 민감한 요소가 R-Cell의 출력 버퍼로 될 수 있다는 것을 나타낸다.

RTAX-DSP의 면역성을 향상시키기 위해, R-Cell은 최근 출력 버퍼에 추가 적인 SET 저감 기법을 통해 향상됐다. 트리플-드라이브로 언급된 솔루션을 사용하면 이 출력 버퍼는 단일 출력 노 드로 연결된 집합성 출력을 통해 3배 증 가된다. 3배 증가된 버퍼 중 하나가 SET를 겪게 된다면, 다른 2개의 버퍼는 과도 상태를 진압하고 정확한 신호를 유지할 것이다. 그 결과, RTAX-DSP R-Cell은 SEE를 완전히 저감시킬 수 있도록 고려된다(그림 2).

RTAX-DSP DSP 매스블록

임베디드 래디에이션 톨러런트 DSP 매스블록(Mathblock)은 18비트×18비 트 멀티플라이 어큐뮬레이트 블록을 갖 는다. 이 블록들은 FIR(Finite Impulse Response)과 IIR(Infinite Impulse Response) 디지털 필터, FFT(Fast Fourier Transform) 및 IFT(Inverse Fourier Transform), DCT(Discrete Cosine Transform), 리드 솔로몬 인코 딩 알고리즘과 같은 DSP 빌딩 블록을 효율적으로 구현하도록 한다. 각각의 DSP 매스블록은 초당 150억 멀티플라 이 어큐뮬레이트(15GMACS)의 총 처리 량을위해125MHz에서동작할수있다. DSP 매스블록의 SET 저감 기법의 경우, 가드 게이트 SET 필터는 멀티플 라이어 출력과 출력 레지스터의 비트 사이에서 각각 인서트된다. 필터의 견 고성을 더욱 강화하기 위해 각 가드 게 이트 또한 3배로 증강된다.

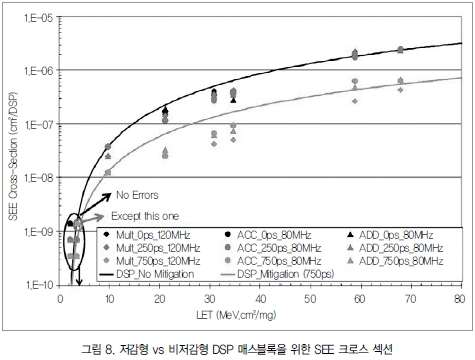

가드 게이트 회로에 있어서 적절한 필터링 강도(또는 지연)를 선택하기 위 해, RTAX4000D의 특별화된 프로토타 입이 개발됐으며 중이온 빔 테스트로 되기 쉽다. 이 특별화된 프로토타입은 RTAX4000D의 생산 버전과 동일하지 만 SET 필터에 대해 다른 양을 추가한 다. RTAX4000D는 코어 타일의 6×5 어레이를 포함하고 있으며, 그 결과 각 각 24개의 DSP 매스블록 5개 칼럼을 보여준다. SET 필터 지연의 양은 컬럼 에 따라 변동된다.

· 컬럼 1 0ps

· 컬럼 2 250ps

· 컬럼 3 500ps

· 컬럼 4 750ps

· 컬럼 5 1,000ps

빔 테스트를 통해 대다수의 SET가 250∼750ps 사이의 펄스 폭을 갖고 있 다는 것을 나타내며, 750ps 필터링의 경우 SEE 크로스-섹션(Cross- Section)에서 눈에 띨 정도로 향상된다. 그 결과, 750ps의 지연값은 RTAXDSP의 생산 버전을 위해 선택된다.

SEE 특성화 결과

RTAX-DSP R-Cell에서 저감 기법 향상에 대해 효율성을 정량화하는 데 있어서, LBNL(Lawrence Berkeley National Laboratories)은 정상적인 결과에서 네온, 아르곤, 구리, 크립톤, 크세논의 중이온 칵테일을 이용하여 광 범위한 중이온 빔 테스트를 수행했다. RTAX-S를 위해 기존에 설계된 테스 트 셋업의 업데이트된 버전이 사용됐 다. 이 셋업은 3가지의 보드 세트로 구 성된다.

① 이온 빔 모니터링과 DUT(Device under Test)의 제어를 담당하는 마스터 FPGA를 포함한 마더보드

② DUT를 하우징하는 RTAX-DSP 도터 보드

③ 중앙 PC와 2개의 USB 포트를 통 한 마더보드간 통신을 위해 슬레 이브 FPGA를 포함하고 있는 인터 페이스 보드

DUT에서 높은 숫자는 병렬식 멀티 플, 비간섭형 테스트 구조의 구성을 가 능하게 하므로 더욱 복잡한 특성을 실 현시켜 준다. 또 이 기법은 각 테스트 구 조가 동일한 조건에서 테스트된다는 것 을 보장한다. RTAX-DSP SEE 특성화의 경우, 설 계는 디바이스의 두 가지 영역에 초점 을 맞춰 구성된다. 즉, FPGA 코어와 DSP 매스블록이다.

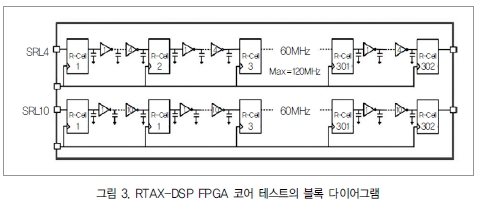

RTAX-DSP FPGA 코어의 특성화

SEE 특성화 코어는 R-Cell 사이에 인서트되는 C-Cell 스트링으로 구성된 테스트 구조를 사용한다. 첫 번째 구조 (SLR4)는 302 R-Cell의 시프트 레지스 터로 구성되며, 각 단계 사이에서 4 CCell의 스트링으로 이루어지고 전부 한 번의 클록으로 구동된다. 두 번째 구조 (SLR10)도 시프트 레지스터이지만, 각 단계 사이에는 10개의 C-Cell 인버터가 있다. 이러한 구조의 기본적인 형태는 RTAX-S 특성화에서 사용되는 구조와 같으며 RTAX-DSP R-Cell에서 저감 향상 회로의 효율성을 직접 비교할 수 있다. 이와 같은 구조는 클록 주파수와 R-Cell 사이에 인서트된 C-Cell 숫자 전 체에서 SEE 크로스 섹션의 의존성을 보 여주기 위해 선택됐다. 최대 주파수가 SRL4일 때 120MHz이며 SRL10일 경우 60MHz가 된다고 해도, 이러한 구조는 모두15 및30MHz에서테스트된다.

테스트가 진행되는 동안, 몇몇 업셋은 15 또는 30MHz에서 구동되는 구조에서 모두 관찰된다. 30MHz에서 이러한 구 조인 SEE 크로스 섹션은 15MHz에서 값을 2배로 만든다. 클록 주파수에서의 리니어 독립성은 대다수의 오류가 SET 이벤트 때문이라는 것을 나타낸다. 또한 동일 주파수(15 또는 30MHz)에서, 데이 터는 10C-R-Cell의 SEE 크로스 섹션 이 4C-R-Cell의 2배가 된다는 것으로 나타내며, 테스트 시 C-Cell의 숫자 기 능이 증가된다는 것을 잘 보여준다.

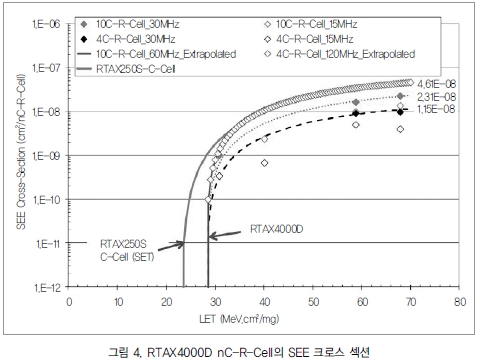

그림 4는 15MHz와 30MHz를 비롯 하여 최대 주파수에서 동작하는 테스트 구조를 위해 선형적으로 추론된 값에서 테스트한 결과를 나타낸 것이다. 이 그 림은 비교를 위한 단일 RTAX-S CCell에 대한 결과도 나타냈다. 최악의 경우, SEE 크로스 섹션이 동시에 일어 나지만 RTAX-S(4.61×10-8cm2/nCR- Cells)에 적합한 C-Cell SET 크로스 섹션은 초과하지 않는다. 게다가 모든 주파수 범위에 있어서 RTAX-DSP에 서 구현되는 nC-R-Cell의 SEE 크로스 섹션은 RTAX-S보다 훨씬 낮다. 데이 터 또한 임계값 LET(LETth)에서 향상 된 28MeV cm2/mg를 나타낸다. 이와 같은 성능 향상은 필터로 동작하는 RTAX-DSP에 대해 라우팅 커패시턴 스가 증가했기 때문일 수도 있다.

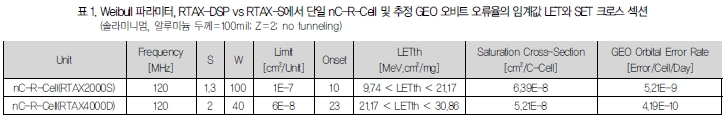

그림 4는 RTAX-DSP R-Cell이 SEE 크로스 섹션에 미치는 영향을 나타낸 것 이며, 트리플-드라이브 저감 기법의 효 율성을 제공한다. 이에 따른 결과로, Weibull 파라미터는 RTAX2000S vs RTAX4000D에서 구현된 nC-R-Cell 에 대해 예측된 지오싱크로너스 오비트 (Geosynchronous Obit) 오류율과 함께 표 1에 나타나 있다. 이 데이터는 RTAX -DSP vs RTAX-S에서 nC-R-Cell의 오비트 오류율 계산 차수에 대한 축소를 나타낸다.

DSP 매스블록의 SEE 특성화

DSP 매스블록의 복잡한 속성에서는 정교한 테스트 기법이 요구된다. 첫째,

3가지 매스블록 컨피규레이션이 각각 테스트돼야 한다. 둘째, 제조 간접비 (Overhead)가 거의 들지 않는 기법이 필요하다. 3가지 컨피규레이션 각각을 위해 2가지 DSP 매스블록이 병렬식으 로 사용되어 골든 레퍼런스로 제시되 며, 다른 하나는 DUT로 제시된다. 모든 3가지 컨피규레이션은 동시에 발생하 는 테스트를 위해 단일 디바이스에 프 로그램되어 있다. 2개의 DSP 매스블록 이 멀리 떨어져서(10㎛ 이상) 배치되므 로, 하나의 클록 싸이클(120MHz에 대 해 8.5ns) 내에서 두 블록에 동시 업셋 이 발생할 가능성은 매우 낮다.

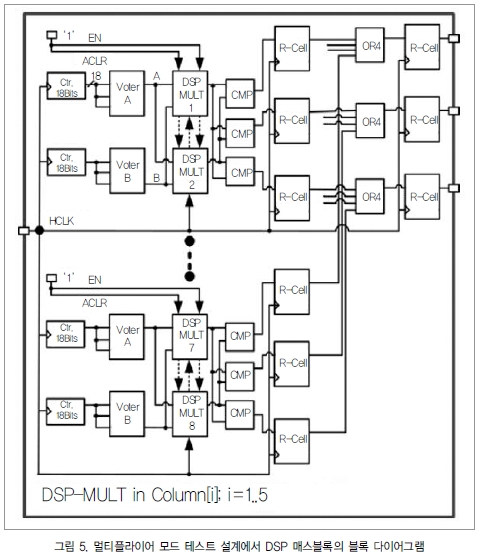

멀티플라이어 모드에서 동작하는 DSP 매스블록을 위한 테스트 셋업

멀티플라이어 모드에서 DSP 매스블 록을 테스트하기 위해, A 및 B 입력은 골든 블록과 DUT 블록 전체에서 동일 한 카운터와 단일 외부 클록으로 구동 된다. 출력은 두 가지 블록에 있어서 각 클록 싸이클에서 비교된다. 높은 신뢰성으로 오류를 감지하기 위 해, 비교 회로(XOR 게이트, R-Cell 등) 는 3배로 된다. 동일한 서브 회로(2개의 블록 세트와 관련된 비교 회로)는 단일 컬럼에서 수직으로 4번 반복된다. 오류 플래그 4개의 3배화된 로직 합계는 마 스터 FPGA로 보내지며, 이것은 3개의 출력이‘0’에서‘1’로 전환될 경우 오류 를 발생시킨다.

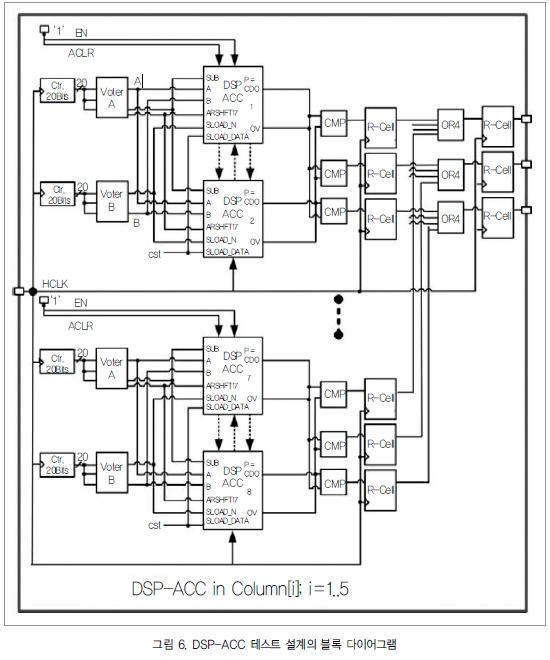

어큐뮬레이터 모드에서 동작하는 DSP 매스블록에 대한 테스트 셋업

어큐뮬레이터 모드 테스트에 대한 DSP 매스블록의 배열은 멀티플라이어 모드일 때의 배열과 유사하다. 카운터 출력은 블록 입력(A와 B)을 순환시킬 뿐 아니라 다른 제어 신호들도(SUB, SLOAD_N 및 ARSHFT17) 순환시킨 다. SLOAD_N의 활성화는 언제든지 2 개 블록의 재동기화를 가능하게 한다. 2 개 블록의 출력은 다시 한 번 각 클록 싸 이클에서 비교된다.

멀티플라이어로서 DSP 매스블록에 대한 테스트 셋업과 유사한 테스트 서 브 회로는 단일 칼럼에서 수직으로 4번 반복된다. 오류 플래그 4개의 3배화된 로직 합계는 마스터 FPGA로 보내진다. 어큐뮬레이터(부하 모드)를 초기화하 기 위해, SLOAD_N 신호는 데이터 (SLOAD_DATA)가 블록의 출력 레지스 터내에로드될수있도록활성화돼야한 다. 이 테스트의 경우, SLOAD_ DATA 는‘0’과‘1’의 로직 상태로 번갈아 구성 되는상수값으로설정된다.

SLOAD_N이 비활성화되어 있을 때, 각 단일 블록은 이에 따른 데이터(P[40 : 0])로 다시 채워져 있으며, 그 다음 어 큐뮬레이터 모드로 동작된다. SUB와 ARSHIFT17 신호는 뺄셈, 덧셈 또는 로 드형/어큐뮬레이트형 데이터 변경 사이 에서 선택할 수 있다. 블록에서 SEE가 발생하면서 어큐뮬레이터 모드에서 동 작할 경우 이벤트는 잠길 수 있으며, SLOAD_N 또는 ACLR 신호의 토클링 만이 이 오류를 제거할 수 있다. 오류 카운터는 로드 모드에서 블록을 동작시키 기 위해 스위치 되자마자 증감하는 과 정을 멈춘다.

DSP 매스블록의 테스트 기간 동안 어큐뮬레이터로서 발생할 수 있는 2가 지 유형의 오류는 다음과 같다

①부하모드에서동작시의단일오류

② 어큐뮬레이터 모드에서 오류 록킹 으로 인한 다중 오류

이와 같은 두 가지 동작 모드 사이에 서 스위칭은 카운터를 통해 SLOAD_N 을 토글링하여 자동화되므로 다중 오류 감지에 따라 모드를 수동으로 리셋하거 나 변경시킬 필요가 없다. 이러한 배열 은 테스트 속도를 향상시키고 두 가지 유형의 오류에 대한 크로스 섹션의 과 소평가 과정을 최소화시킬 뿐만 아니라 2가지 유형의 오류 사이에서 차별화 과 정을 발생시킨다.

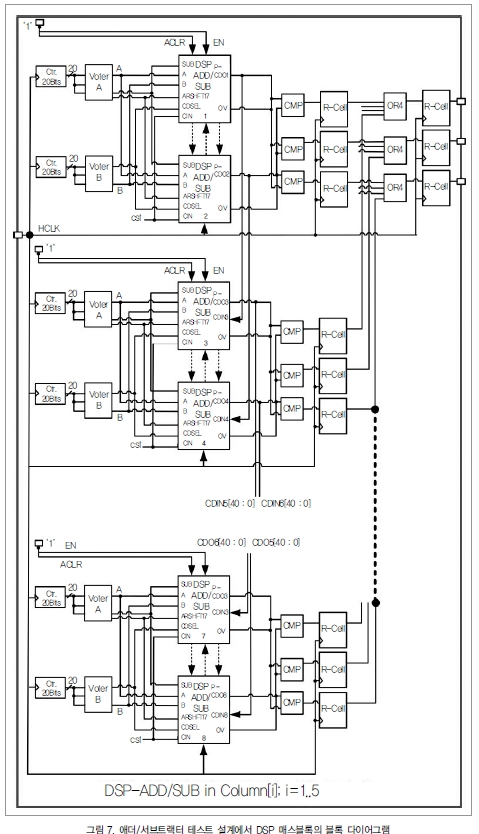

애더/서브트랙터 모드에서 작동하는 DSP 매스블록을 위한 테스트 셋업

4개의 DSP 매스블록은 비교기와 체 인에서 다음 블록의 CDIN 두 가지로 채 워지는 출력(CDO)과 함께 체인된다. 이 두 가지 체인은 인터리브되므로 각 단계 는 다른 컨피규레이션으로 하나의 골든 과 하나의 DUT인 한쌍의 블록을 갖게 된다.

애더/서브트랙터 모드에서 블록은 CDSEL이 활성화되었을 때 CIN 값으 로 초기화된다. CDSEL이 비활성화됐 다면 DSP 출력 레지스터는 체인에서 기존 DSP 블록의 CDIN으로 채워져 있 다. 최초 DSP 블록의 CDIN은 마이크 로 세 미 Libero IDE (Integrated Design Environment) 설계 소프 트웨어를 통해‘0’로직 상 태로 자동 설정된다. 각 쌍 의 DSP 블록 출력과 초과 된 신호를 비교하고 오류 플래그는 마스터 FPGA로 다시 전송된다. 이 경우, 여 러 개의 오류는 SEE가 체 인에서 1차, 2차 또는 3차 DSP로 발생할 경우에만 나타난다.

빔 테스트 결과

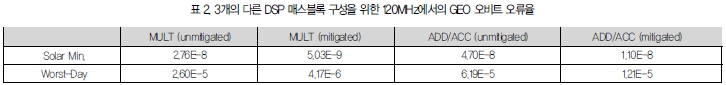

출력 상태에서 SET 필터 링 효과를 측정하기 위해, DSP 매스블록의 3가지 컨 피규레이션에 대해 저감되 지 않은 버전과 저감 버전 모두 테스트를 실시했다. 3 가지 컨피규레이션은 주파 수에서 분명한 독립성을 가 지고 SEE 민감도를 보여준 다(그림 8). 실제로 블록에대한 SEE 크로스 섹션은 주파수와 거의 선형으로 증가된다. 동일한 주파수 에서, 크로스 섹션은 모든 3가지 컨피규레이션에 있 어서 유사하지만 멀티플 라이어 모드에서보다 어 큐뮬레이터 혹은 애더/서 브트랙터 모드에서 더 높 다. 애더/서브트랙터와 멀 티플라이어 모드 사이의 크로스 섹션 차이는 피드 백 경로에서 추가적인 통 합 로직 때문인 것 같다. 한편, 애더/서브트랙터 및 어큐뮬레이터 모드에서 측정된 크로스 섹션의 유 사성은 두 가지 모드에서 민감한 모드의 동일한 숫 자이기 때문인 것 같다.

이 데이터는 완환 기법 이 사용된 설계와 비저감 기법이 사용된 설계에서 SEE 크로스섹션의 향상 을 확실히 나타낸다. 표 2 는 두 가지 버전에 대한 추측용 GEO 오비트 오류 율을 나타낸 것이다.

RTAX-DSP FPGA는 래디에이션 톨러런트 FPGA 제품군을 위한, 현 재 골드 표준인 RTAXS/ SL FPGA의 최종 변형 제품이다. 마이크로세미 의 최신 래디에이션 톨러 런트 FPGA 제품들은 임 베디드 래디에이션 톨러런트 멀티플라이 어큐뮬레이트 블록 (DSP 매스블록)을 RTAX-S 구조에 추 가했다. RTAX-S는 설계가 강화된 DSP 블록 래디에이션이 포함된 최초의 FPGA이다.

DSP 기능을 포함하여 새로운 디바이 스는 성능이 향상됐으며 더욱 강화된 플 립플롭을 통합하고 있고 RTAX-S/SL 디바이스가 제공하는 견고한 수준 이상 의 SEE에 대한 보호 기능을 제공한다. RTAX 제품군에 대한 두 가지 기능이 새로 추가되어 매우 낮은 궤도 오류율을 나타내는 고집적, 고성능 래디에이션 톨 러런트 솔루션이 탄생했다.

참 고 문 헌

1. RTAX-DSP Radiation-Tolerant FPGAs,product brief

2. RTAX-S/SL RadTolerant FPGAs,datasheet

3. SEE Characterization of the New RTAXDSP(RTAX-D) Antifuse-Based FPGA,Sana Rezgui, Paul Louris, and Rezwana Sharmin. July 2010. Submitted for publication.

4.“ SET Characterization and Mitigation in RTAX-S Antifuse FPGAs”, IEEE Aerospace Conference,

S. Rezgui, J.J. Wang, Y. Sun, D. D'Silva, B.Cronquist and J. McCollum. Mar. 2008.