[첨단 헬로티]

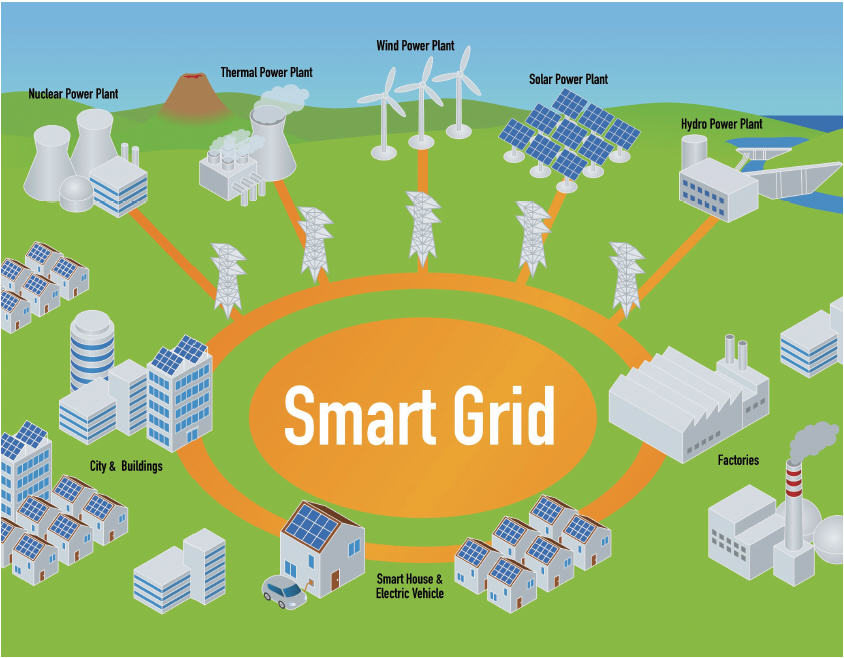

전세계 전력 인프라는 발전, 송전, 배전 등 시스템들의 상호 연결로, 흔히 ‘파워 그리드’라 한다. 전체의 신뢰성과 이용률 및 효율을 늘리기 위해 통신과 추가 센서들이 더해지면서 파워 그리드가 이른바 스마트 그리드로 더욱 똑똑해지고 있다. 변전소는 스마트 그리드 인프라의 핵심 구성요소이며, 주거 및 상업지에 서비스를 제공하는 저전압 피더 등 송전 및 배전을 따라 위치한다. 변전소는 송전을 위해 전압 레벨을 변환하고 피더 스위칭, 로드 스위치 부하, 차단기 보호 및 자산에 대한 지속적인 모니터링 등과 같은 중요한 기능을 수행해, 이용률과 효율을 높여 중단시간을 줄인다.

그리드에 사용되는 주요 핵심 장치 중 하나가 오작동 보호 계전기(Protection relay)다. 오작동 보호 계전기는 보호 및 제어 기능을 구현하고, 발전기, 송전선, 모터, BUSBAR, 기타 그리드 장비를 보호하도록 구성 가능하다.

오작동 보호 계전기는 스마트 그리드에서 다음과 같은 역할을 한다:

• 그리드의 비정상적인 파워 시스템 동작을 감지해 경고를 보내고 필요한 조치를 취한다.

• 아날로그 입력을 샘플링하고 연결된 장비의 전기 파라미터들을 계산하며, 보호를 위해 회로 차단기에 트립 신호를 제공하는 등 이미 구성된 기능을 바탕으로 조치를 취한다.

• 발전, 송전 및 배전 등 파워 시스템의 효율과 신뢰성을 개선한다.

• IEC 61850(international Electrotechnical Commission) 및 IEC 62439 표준 요건에 따라, HSR(High-Availability Seamless Redundancy)/PRP(Parallel Redundancy Protocol) 같은 통신 인프라를 통해 중앙 모니터링 시스템으로 상태 업데이트를 보낸다.

보호 계전기는 AC 아날로그 모듈로 구성된다. 복수의 전압 및 전류 입력이 아날로그 입력 모듈에 연결되며, 그 입력들을 ADC 범위에 맞춰 조정한 후 고정밀 ADC를 이용해 그 아날로그 입력들을 디지털 값으로 변환한다. 이 프로세서 모듈은 아날로그 입력 모듈에서 샘플링 된 디지털 값들을 획득한 후 디지털 필터링 등 그 샘플 데이터를 처리하고, 전기 파라미터들을 계산하고, 보호 알고리듬을 실행하고, 그 파라미터들을 중앙 네트워크로 전달한다. 이 백서에서는 보호 계전기의 프로세서 모듈에 대해 중점적으로 다루고자 한다.

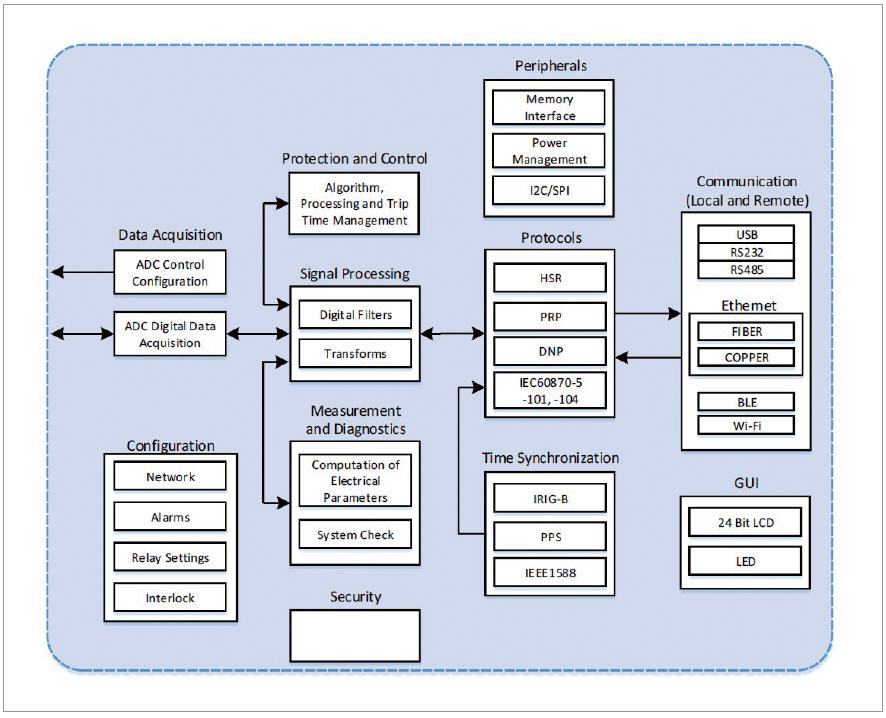

보호 계전기의 프로세서 모듈은 일반적으로 [그림 1]처럼 샘플을 수집, 그 데이터를 처리 및 전송하고, 추가적으로 HMI와 진단에 필요한 기능을 제공한다.

▲ 그림 1. 보호 계전기의 프로세서 모듈 내 전형적인 데이터 흐름

이 프로세서 모듈은 직렬/병렬 인터페이스를 이용해 ADC(Analog-to-Digital Converter)에서 디지털 데이터를 수집하고 그 데이터를 신호처리를 위해 제공하는데, 디지털 필터링을 실시해 그 입력 신호를 다듬은 후 변칙을 제거한다.

필터링 된 데이터는 프로세싱 보호 알고리듬으로 옮겨지는데, 여기에는 애플리케이션별 알고리듬의 처리가 수반된다. 이 알고리듬은 모니터링 된 파라미터들이 범위 내에 있는 지를 판단한 후, 과부하, 디퍼렌셜, 역전력 등과 같은 최종 장비별 보호 요건에 대해 데이터를 분석하고, 트립 신호를 회로차단기로 보내며, 미리 정해놓은 타이밍이 기준 트립 곡선을 따르도록 한다. 또한 이 필터링 된 데이터는 측정 및 진단에 쓰이는 전기 파라미터들을 계산하는 데에도 사용된다.

통신 장치는 서로 다른 통신 인터페이스들과 HSR/PRP 같은 중복 프로토콜을 포함해 필수의 프로토콜들을 실행하고, 이벤트와 상태를 SCADA 관리 제어 데이터 획득 시스템 같은 상위 레이어로 보고한다. 그래픽 LCD는 이 파라미터들의 상태와 보호 대상 장비를 그래픽 형태로 제공해 신속한 분석을 가능하게 한다.

보호 계전기에서 프로세서 모듈이 처리하는 문제들

기존의 그리드가 스마트 그리드로 나아가고 스마트 그리드의 배치가 늘어남에 따라, 이 프로세서 모듈은 다음과 같은 문제들을 처리한다:

• 서로 다른 인터페이스와 프로토콜로 복수의 외부 ADC들과 인터페이스 한다.

• 취득한 ADC 데이터를 처리해 최고의 AC 성능을 달성한다.

• 멀티코어 서브시스템을 이용해 고급 DSP(digital signal processing), 변환 및 데이터 관리 등의 기능을 수행한다.

• HSR/PRP 같은 중복 산업 이더넷 프로토콜들을 지원한다.

• 직관적이고 풍부한 HMI(human machine interface)를 제공한다.

• 높은 신뢰성, 긴 POH(power-on hours) 및 풀 ECC(error-correction code)

• 첨단 보안 기능들과 기능 안전을 지원한다.

• 복수의 직렬 및 병렬 인터페이스들과 연결하기 위한 광범위한 주변장치 세트

오작동 보호 계전기 프로세서 모듈

애플리케이션을 위한 -Sitara AM6x 디바이스

이 프로세서 모듈이 여러 가지 프로세싱 필요성과 문제들을 해결하려면 복수의 프로세싱 서브시스템이 필요할 수 있다. 디바이스의 수를 줄여 기능을 병합하거나, 단 하나의 디바이스에 기능을 병합하면 시스템 비용과 복잡도를 줄일 수 있다.

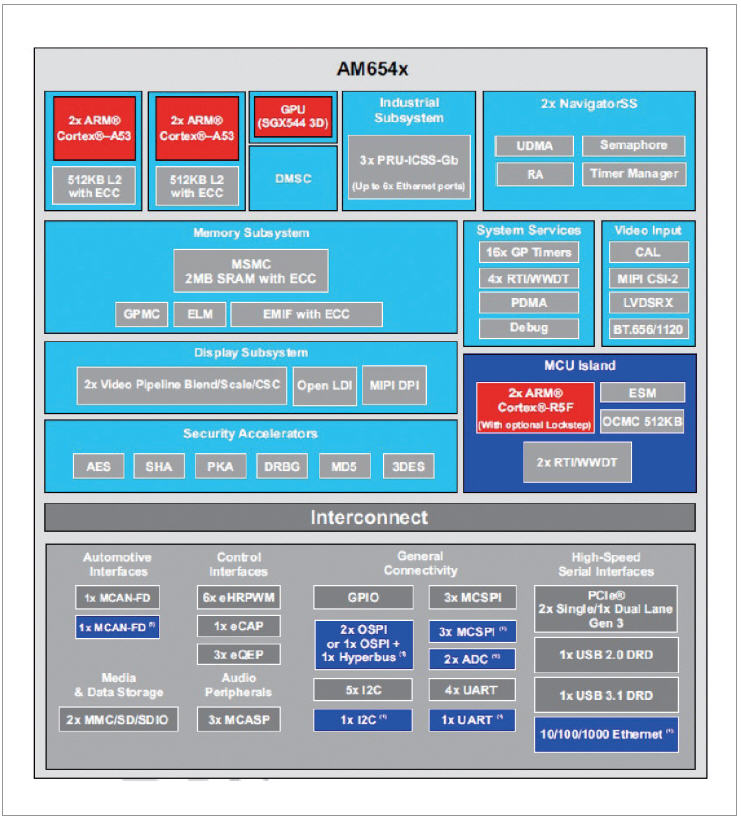

텍사스인스트루먼트(TI)의 Sitara AM6x 프로세서는 보호 계전기의 프로세서 모듈에 적합하도록 설계된 단일칩 솔루션이다. [그림 2]는 AM6x 프로세서 제품군 중 하나인 AM654x 프로세서의 블록 다이어그램이다.

▲ 그림 2. AM654x 프로세서 블록 다이어그램

[그림 2]에 나열된 문제들을 AM6x 프로세서의 기능들과 연결해보자.

서로 다른 인터페이스 및 프로토콜로

외부 ADC로부터 고속 고성능 데이터를 획득

프로세서 모듈의 주요 과제 중 하나는 SPI(Serial Peripheral Interface) 등 서로 다른 인터페이스 옵션들과 일관된 샘플링을 구현하기 위해 입력 주파수 기반의 변화하는 타이밍 요건들을 이용하고 복수의 외부 ADC들을 동시에 연결할 수 있다는 것이다. 상황을 더욱 복잡하게 만들기 위해, 수많은 제조사들은 프로세서에서 데이터를 수집하기 위해 커스텀 타이밍이 필요한 ADC 인터페이스를 만들었다.

TI AM6x 프로세서는 복수의 ADC를 인터페이싱 하는 문제를 PRU-ICSS(Programmable Real-time Unit subsystem and Industrial Communication Subsystem) 주변장치로 해결하고 있다. PRU-ICSS는 외부 ADC들에 직접 연결해 BOM 비용을 절감할 수 있다. 그리고 신호체인 성능을 개선하고 ADC 인터페이스가 일관된 샘플링을 달성하는데 필요한 타임 베이스를 조정함으로써 스펙트럼 누출을 줄인다.

고급 DSP 및 데이터 관리 기능을 위한 멀티코어 프로세싱 실시

고급 신호 처리 및 관리 기능 등의 고성능 처리 요건을 충족하기 위해, AM6x 디바이스 제품군은 NEON 확장이 가능한 최대 4개의 Arm Cortex-A53 코어 및 듀얼 Arm Cortex-R5F 마이크로컨트롤러(MCU) 서브시스템과 결합한다. Cortex-A53 코어는 공유 L2 메모리가 있는 듀얼 코어 클러스터에 배치되어 2개의 고성능 처리 채널을 생성한다. Cortex-R5F 코어는 보호 계전기 관리 및 이더넷 통신 기능에 필요한 성을 제공하는 반면, 통합형 TCM(tightly coupled memories)가 있는 Cortex-A53 코어는 ADC 샘플 데이터 필터링 및 DSP 기능에 쓰일 수 있다.

HSR/PRP 같은 중복 산업 프로토콜을 포함한 이더넷 프로토콜의 지원

변전소 자동화를 위한 이더넷 네트워크에는 높은 신뢰성과 예측성이 필요하다는 점 때문에 IEC 62439 표준이 등장하게 되었다. 이것은 저비용의 유지관리가 편리하고 상호작동이 가능한 통신 네트워크 인프라를 구축하고자 한다. IEC 62439-3 제4절과 제5절이 HSR(High-availability Seamless Redundancy)과 PRP(Parallel Redundant Protocol)를 규정하고 있다.

AM6x 프로세서는 PRU-ICSS 기술을 이용해 HSR/PRP를 지원한다. 그 구현은 PRU-ICSS 펌웨어와 드라이버들(Linux/실시간 운영 체재[RTOS]), 애플리케이션과 심플 네트워크 관리 프로토콜 지원 등으로 구성되어 있다. PRU-ICSS 펌웨어가 링크 중복을 다룬다면, 호스트(Cortex-A53)는 드라이버와 애플리케이션 코드를 실행한다. TI는 PRU-ICSS HSR 펌웨어와 드라이버들(Linux 및 TI-RTOS)을 무상으로 제공하고 있다. AM6x PRU-ICSS는 기가비트 HSR/PRP를 지원하도록 업그레이드됐다.

UART/SPI 포트를 이용해 추가로 비동기식 통신이나 동기식 통신 인터페이스를 구현하고, PRU-ICSS를 이용해 범용 비동기식 리시버 트랜스미터 포트나 SPI 포트를 추가할 수도 있다. 또한 PRU-ICSS 코어를 커스텀 다목적 입력·출력 조작과 심층 패킷 점검에 사용할 수도 있다.

직관적이고 풍부한 HMI의 제공

오작동 보호 계전기에는 직관적인 HMI를 가진 그래픽 LDC가 통합돼 있어, 파형, 트렌드, 전기 파라미터들, 구성 및 상태 등을 볼 수 있다. 풍부한 HMI는 교육 비용을 줄이고 분석을 간소화하며 구성 오류 가능성을 최소화 시켜 준다. AM6x 프로세서에는 LCD 컨트롤러와 3D 그래픽 가속기가 집적되어 있어 HMI 기능을 풍부하게 구현할 수 있다.

높아진 신뢰성과 진단 능력

보호 계전기에는 높은 신뢰성과 긴 수명이 필요하며, 극한의 환경에서 작동해야 하는 경우가 많다. AM6x 프로세서는 이러한 요건들을 충족하도록 만들어졌다. 메모리의 광범위한 ECC 범위와 로직의 고장을 적시에 제한할 수 있는 설계 전략은 복잡한 시스템온칩에 필요한 가장 낮은 총 소프트 오류율을 가능하게 해준다.

AM6x 프로세서는 -40℃~105℃의 접합 온도(Tj)에서 정격 산업 온도를 가지고 있다. 최대 Tj 105℃에서 AM6x 프로세서는 예측 작동 수명이 100,000 POH이며, 모든 Cortex-A53 코어는 1.0GHz에서 작동하고 나머지 디바이스들은 최대 주파수에서 작동한다.

산업용 애플리케이션에서 흔히 볼 수 있는 또 다른 요건은 100,000 POH 이상의 디바이스 작동 수명이다. 95℃보다 낮은 Tj를 다룰 수 있는 애플리케이션의 경우, AM6x 프로세서는 예측 수명을 최대 200,000 POH까지 제공하고 있다.

AM6x 프로세서에는 지속적으로 작동하는 광범위한 하드웨어 진단 기능이 포함돼 있다. 그 예들로는 Cortex-R5F 아키텍처와 메모리 관리 유닛, 방화벽, 메모리 및 인터커넥트를 위한 싱글 및 더블 오류 검출 패리티, 파워 서플라이 진단, 온도 센서 및 리셋 진단 등이 있다. AM6x 안전 매뉴얼에 이 진단 기능들이 자세히 나와 있다.

첨단 안전 기능들과 기능 안전의 지원

기능 안전은 그리드 인프라를 보호하는 마지막 방어선이기 때문에, 보호 계전기에서 새롭게 떠오르고 있는 요건이다. 기능 안전은 시스템 설계자가 컴포넌트 장애를 빠르게 진단하고 피해를 방지할 수 있는 시스템의 능력을 더 많이 신뢰할 수 있도록 해준다. TI는 AM6x 프로세서에 기능 안전 이네이블러와 풀 ECC 요건들을 설계했다.

AM6x 프로세서는 IEC 61508 SIL(Safety Integrity Level) 3의 목표 레벨을 가진 산업 제어 애플리케이션에 사용할 수 있다. TI는 AM6x 프로세서를 통합하는 시스템의 기능 안전 요건을 충족하면서 체계적이고 무 무작위인 장애를 관리할 수 있도록 SafeTI 디자인 패키지를 제공한다. 표준들이 요구하는 대로, TI는 외부에서 인증 받은 하드웨어 및 소프트웨어 개발 프로세스와 추적, 기록 및 검증 요건들도 따른다.

TI가 제공한 소프트웨어 규격 패키지 및 컴파일러 검정 키트가 체계적인 시스템 장애를 관리한다. 무작위 장애의 경우, TI는 구성 가능한 AM6x 장애 모드 효과 및 진단 분석 툴을 제공해, 이 디바이스의 설계 및 진단 범위에서 장애 모드들과 지표들을 상세히 제시한다. 또한 SafeTI 패키지는 안전 분석 보고서를 제공하고 있다. 이 보고서는 정황과 상관없이 안전 구성요소로, AM6x 프로세서를 제3자가 평가한 것을 인증 요약한 것이다.

그리드 인프라 공격에 대한 우려가 사상 최고치이다. 보안 위협은 항상 존재하며, 스마트 그리드에서 사물 인터넷이 빠르게 확산됨에 따라 이러한 위협은 어디에서든 등장하고, 심지어 눈에 띄지 않는 저가의 엔드노드 디바이스에서도 나타날 수 있다. 문제는 시스템에 대한 공격 유무가 아니라 그 시기다. 보안은 보호와 마찬가지로 리스크 관리만큼이나 중요하다. 보호 계전기가 공격 받을 수도 있다는 점을 감안하면, 시스템 설계자는 보안을 최우선 순위로 삼아야 할 것이다.

소프트웨어 및 하드웨어 보안 기능들은 서로 함께 작동하는 것이 독립적으로 작동하는 솔루션보다 더 안전한 보호 레이어를 제공한다. 물론, 보안 아키텍처의 강점은 보안 아키텍처의 기반에 좌우될 것이다. 기초 레이어의 4가지 요소들이 특히 중요한데, 보안 부트 프로세서, 디버깅 보안, 하드웨어 기반 디바이스 키·ID, 암호 가속이다. AM6x 프로세서는 보안 부트, 디버깅 보안, 키·ID, 암호 가속, TEE(Trust Execution Environment), 보안 스토리지, 네트워크 보안 소프트웨어 IP(Intellectual Property) 보호, 초기 보안 프로그래밍, 보안 펌웨어 및 소프트웨어 같은 보안 기능들을 제공한다.

프로세싱 모듈 BOM

BOM 절감은 언제나 프로세서 모듈의 우선사항이다. BOM 비용을 낮추는 한 가지 방법은 사용하는 디바이스의 수를 줄이는 것이다. 이것은 컴포넌트들과 관련 PCB(Printed Circuit Board) 비용을 절감하게 해준다. 컴포넌트 수가 줄어든다는 것은 설계가 간소해지고 PCB 라우팅 문제가 줄어든다는 것을 의미한다.

AM6x 프로세서는 PRU-ICSS를 통합해, 외부 ADC들에 FPGA(Field-programmable Gate Arrays)를 연결할 필요가 없다. 동일한 PRU-ICSS 주변장치를 이용해 HSR/PRP 같은 중복 프로토콜들을 구현할 수도 있다. 통합된 LCD 컨트롤러와 3D 그래픽 가속기, 고성능 멀티코어 아키텍처가 어우러진 AM6x 프로세서는 프로세서 모듈에 적합하다.

AM6x를 이용한 프로세서 모듈 사례

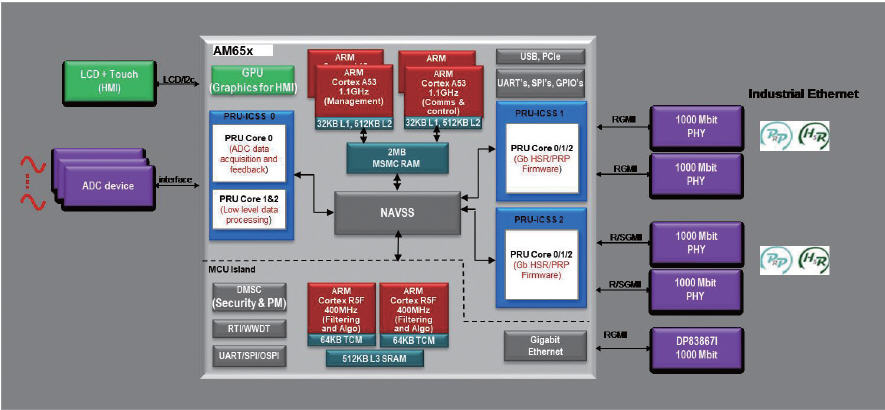

[그림 3]은 AM6x 프로세서 기반 오작동 보호 계전기의 한 예이다. 외부 ADC들은 SPI나 멀티-SPI를 모방할 수 있는 인터페이스 신호를 이용해 바로 PRU-ICSS에 연결된다. PRU-ICSS는 PRU-ICSS 펌웨어 제어 하에서 ADC 구성 및 데이터 수집을 실시한다. 이 펌웨어는 선택한 외부 ADC에 따라 맞춤 설정이 가능하다.

▲ 그림 3. AM6x 프로세서 기반 보호 계전기의 시스템 블록 다이어그램

AM6x 프로세서는 PRU-ICSS 서브시스템의 3개의 인스턴스를 포함한다. 하나는 ADC 인터페이스에 쓰이며, 2개 PRU-ICSS 서브시스템을 HSR/PRP 프로세싱을 위해 남겨뒀다. 각각의 PRU-ICSS는 2개의 이더넷 포트를 지원하므로 총 4개의 이더넷 포트를 지원한다.

AM6x PRU-ICSS의 3가지 RISC 코어는 250MHz에서 실행되며, 제로-크로스 감지와 임펄스 응답 필터링 같은 로우레벨 프로세싱 애플리케이션을 가능하게 한다. 필터링 된 데이터는 하드웨어 다이렉트 메모리 액세스 엔진을 이용하는 광범위한 상호 프로세스 통신을 통해 Cortex-R5F 서브시스템 메모리로 전달된다.

AM6x 프로세서에는 400MHz에서 실행되는 듀얼 Arm Cortex-R5F MCU가 포함되어 있으며, 필터링, 표준화, 최종 장비별 알고리듬 처리 같은 실시간 기능들을 수행할 수 있다. 각각의 Cortex-R5F 코어마다 빠른 데이터 접속을 위한 64KB TCM이 있다. 최종 장비 별 동작과 처리는 이 서브시스템에서 일어날 수 있는데, 그 이유는 Cortex-R5F가 결정론적 능력을 가진 실시간 프로세싱 코어이기 때문이다.

또한 AM6x 프로세서에는 일반적인 애플리케이션 관리를 실시하고, 통신 프로토콜 스택을 실행할 수 있는 쿼드 Arm Cortex-A53 프로세서 코어가 있다. 각각의 코어는 최대 1.1GHz 속도에서 실행될 수 있으므로, 복잡한 스택 및 관리 프로토콜에 필요한 컴퓨팅 성능을 제공한다.

결론

AM6x 프로세서는 오작동 보호 계전기의 프로세서 모듈을 위한 단일칩 솔루션을 제공하며, 외부 ADC들과 직접 인터페이싱 하고, 복수의 통신 인터페이스 및 프로토콜들을 구현할 수 있다. PRU-ICSS를 이용해 맞춤형 인터페이스 및 프로토콜을 제공할 수 있기 때문에, FPGA가 ADC와의 인터페이싱을 처리해야 필요가 없다.

AM6x 프로세서는 PRU-ICSS를 이용해 추가로 기가비트 HSR/PRP 프로토콜도 지원하며 그 펌웨어는 TI에서 무상으로 제공된다. AM6x 프로세서에는 PRU-ICSS의 3개의 인스턴스가 있는데, ADC 연결이나 인스턴스 당 2개의 포트 HSR/PRP에 사용할 수 있다.

AM6x 프로세서의 통합형 LCD 컨트롤러와 3D 그래픽 가속기는 온디바이스 교육 비디오와 함께 디바이스의 상태 및 구성을 제공하는 다양한 HMI 기능에 대한 보호 계전기의 현재 트렌드에 잘 맞는다. AM6x 프로세서는 외부 연결 디바이스 없이도 주변장치를 바로 연결할 수 있도록 복수의 UART, SPI, I2C, McASP, USB, PCIe(Peripheral Component Interconnect Express) 등 충분한 커넥티비티 옵션들을 제공하고 있다.

AM6x 프로세서의 신뢰성 및 기능 안전 기능들에는 디바이스 전체 메모리의 풀 ECC, 온칩 메모리에 포함된 광범위한 하드웨어 진단, 주변장치들, 인터커넥트 등이 있다. 전체적으로 이 프로세서에는 IEC 61508의 SIL 3레벨까지 달성할 수 있도록 시스템의 설계를 돕기 위한 기능들도 포함돼 있다.

AM6x 프로세서는 보안 부트, 디버깅 보안, 키·ID, 암호 가속, TEE, 보안 스토리지, 네트워크 보안, 소프트웨어 IP 보호, 초기 보안 프로그래밍, 보안 펌웨어 및 소프트웨어 같은 보안 기능들을 통해 보호 계전기를 악의적 공격으로부터 방어할 수 있다.

글 : Amrit Mundra, Bryan Trinh, Sreenivasa Kallikuppa, Prasanna Rajagopal 텍사스 인스트루먼트 연구원