클로킹 요구가 다른 통합 칩들을 포함한 시스템 보드를 설계할 경우, 설계상 각각의 타이밍 요구를 이해하는

것이 중요하다. 디자이너들은 칩으로 지터와 클록 주기를 비롯, 다양한 타이밍 제약을 충족하는 클록 신호를

제공해야 한다. 다중의 프로그래머블 출력을 지원하는 최신 프로그래머블 클록 제너레이터를 이용하면 다양

한 시스템 타이밍 요구를 충족할 수 있으며, 향후 시스템 발전에 따른 성능 요구에도 대응할 수 있다.

오늘날 복잡한 시스템 보드는 애플리케이션 프로세서, 고성능 범용 프로세서, 다중의 시스템온칩(System-on-a-Chip)을 포함하고 있다.

이러한 고성능 회로들은 애초에 함께 작동할 것을 고려하여 설계된 것이 아니므로 각각 클록 주파수 요구가 다를 수 있다. 뿐만 아니라 보드 상의 회로들은 각각 클록 안정성(지터)과 클록 주기 비율(듀티 사이클)을 비롯한 타이밍 제약이 다를 수 있다.

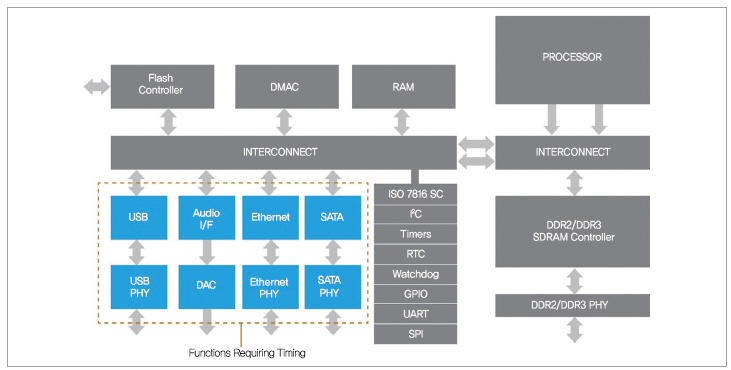

그림 1. 셋톱박스의 블록 다이어그램 (클록 주파수와 클록 안정성 요구가 각각 다른 다수의 회로 기능들을 포함하고 있다.

통상적으로는 다수의 타이밍 신호를 제공하기 위해 다중의 클록 오실레이터를 이용한다)

따라서 이와 같이 복잡한 보드에서는 각각 칩들에 제공하기 위한 다중의 시스템 클록 신호를 발생시키고, 다수 서브시스템의 타이밍을 관리하기 위한 클로킹 서브시스템을 설계하는 것이 중요한 설계 과제가 되었다(그림 1). 이러한 보드는 셋톱박스/DVR, 하이엔드 디지털 TV, 네트워크 스위치 및 라우터, 데이터 서버 등과 같은 다양한 유형의 애플리케이션에 통상적으로 이용되고 있다.

하지만 최대의 타이밍 마진을 확보하고자 다중의 클록을 동기화하기 위해서는 다중의 프로그래머블 클록 출력을 제공하면서 지터가 낮은 클록 소스가 필요하다. 보드 상에서 다중의 개별적인 크리스털 오실레이터를 이용할 경우 간편하게 동기화할 수 없으므로, 이제 더 이상 신뢰할 수 있는 솔루션이라고 할 수 없게 되었다.

뿐만 아니라 단일 보드에 많게는 5∼6개의 크리스털 및 CMOS 크리스털 오실레이터를 이용하는 것은 제조 원가를 높일 뿐만 아니라 EMI 억제 측면에서 확산 스펙트럼 기능을 제공하지 못한다.

그러므로 보드 상 다수의 서브시스템으로 동기화된 클록 신호들을 제공하기 위해서는 다중의 PLL(Phase-Locked Loop) 제어 출력을 제공하는, 고도로 통합된 클록 소스를 이용하는 것이 좋다. 이러한 솔루션은 보드 공간을 절약하고 설계 복잡성을 낮추며 시스템 비용을 낮출 수 있다.

또한 오늘날 클록 신호는 무결성을 떨어트리지 않으면서도 회로 보드 상에서 긴 배선 경로를 통과할 수 있어야 한다. 배선이 길어지면 스위칭 잡음이 유입될 수 있고 커패시티브 로딩으로 인해 신호 저하를 일으킬 수 있으며, 인쇄 회로 보드 상에서 비정상적으로 긴 배선 때문에 지연 문제를 겪을 수도 있다.

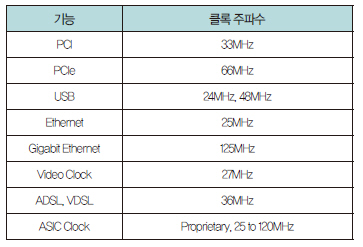

셋톱박스와 같은 시스템에서는, 다수의 서브시스템 블록이 표 1과 같이 자신이 시행해야 하는 시스템 기능에 따라 각각 다른 주파수로 동작한다.

표 1. 셋톱박스에서 주요 시스템 기능의 클록 주파수

PCI나 PCIe 같은 인터페이스는 필요로 하는 데이터 전송 속도에 따라 한 주파수 또는 기본 주파수의 배수로 동작한다. USB 인터페이스 역시 마찬가지이며, 이더넷은 데이터 속도에 따라 다중의 주파수로 동작한다. 비디오 신호나 메인 ASIC/프로세서 같은 기능들 역시 각각 요구하는 클록으로 동작한다.

시스템 애플리케이션과 상관 없이, 지터(Jitter)는 모든 시스템 디자이너에게 공통적으로 중요한 과제이다. 그 이유는 지터의 경우 회로 보드에서 제공하고자 하는 다중 클록 신호의 타이밍 마진에 부정적으로 영향을 미치기 때문이다. 뿐만 아니라 데이터 속도와 시스템 클록이 갈수록 더 높아지고 있으므로, 타이밍 지터는 시스템 설계에서 중요하게 고려해야 할 요소가 되고 있다. 대부분의 경우, 시스템 타이밍 마진이 시스템 성능의 한계를 결정한다. 그러므로 시스템 설계에서는 타이밍 지터에 대한 충분한 이해가 더욱 더 중요해지고 있다.

총 지터는 랜덤 지터 성분과 확정적 지터 성분으로 이루어진다. 클록 타이밍 지터는 시간 도메인과 주파수 도메인으로 측정할 수 있다. 피리어드 지터(Period Jitter), 사이클 대 사이클 지터(Cycle-to-Cycle Jitter), TIE 지터(Time Interval Error Jitter)는 시간 도메인으로 측정하고, 위상 잡음과 위상 지터는 주파수 도메인으로 측정한다. 지터를 유발하는 요인으로는 열 잡음, 전원장치 잡음, 누화, 신호 반사 등이 있다.

다양한 형태의 지터

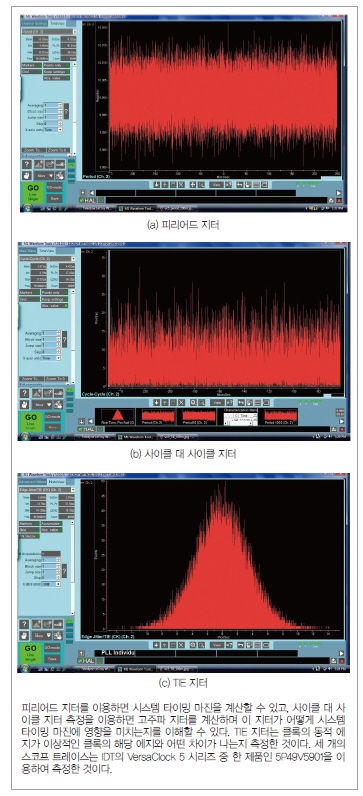

그림 2. 클록 신호에 나타날 수 있는 세 가지 지터 형태

클록 지터는 크게 세 가지 형태로 구분할 수 있으며, 어떤 하나의 시스템에 이 세 가지 형태가 모두 존재할 수도 있다. 실제 지터를 보여 주기 위해 그림 2에 나타난 스코프 트레이스는 IDT의 VersaClock 5 시리즈의 클록 제너레이터 칩인 5P49V5901을 이용해 포착했다.

그러면 각각의 지터에 대해 살펴보고, 시스템 성능에 어떻게 영향을 미치는지 알아 보자.

1. 피리어드 지터

피리어드 지터는 10,000 클록 사이클에 걸쳐 파형 클록 사이클의 클록 주기 최대 편차를 측정한 것이다[그림 2(a)]. 그리고 피리어드 지터의 RMS 값은 10,000 클록 사이클에 걸쳐 클록 주기의 표준 편차를 측정한 것이며, 피리어드 지터의 피크 투 피크 값은 10,000 클록 사이클에 걸쳐 최소 클록 주기와 최대 클록 주기의 차를 측정한 것이다.

10,000 클록 사이클에 걸쳐 클록 주기의 편차를 측정하고 이 피리어드 지터 측정을 이용하면 애플리케이션의 저주파 지터를 계산할 수 있다. 그리고 피리어드 지터를 이용해서 시스템 타이밍 마진을 계산할 수 있다. 그림 2(a)에서 RMS 측정 값은 4.7ps이고 피크 투 피크 측정 값은 41.81ps인 것을 알 수 있다.

2. 사이클 대 사이클 지터

사이클 대 사이클 지터의 RMS 값은 1,000 클록 사이클에 걸쳐 인접한 클록 사이클 두 개 사이의 클록 주기 변화를 측정한 것이다(표준 편차). 사이클 대 사이클 지터의 피크 투 피크 값은 1,000 클록 사이클에 걸쳐 인접한 클록 사이클 두 개 사이의 최소 클록 주기 변화와 최대 클록 주기 변화의 차를 측정한 것이다[그림 2(b)].

사이클 대 사이클 지터 측정 값을 이용하면 애플리케이션의 고주파 지터를 계산할 수 있다. 시스템 타이밍 마진에 미치는 영향을 최소화하려면 이 값을 가능한 한 작게 해야 한다. 그림 2(b)에서 사이클 대 사이클 지터의 RMS 측정 값은 4.42ps이고 피크 투 피크 측정 값은 37.03ps이다.

3. TIE 지터

TIE 지터는 클록의 동적 에지가 이상적인 클록의 해당 에지와 어떻게 차이가 나는지 측정한 것이다[그림 2(c)].

TIE 지터의 RMS 값은 이 타이밍 오차의 표준 편차를 나타낸다. TIE 피크 투 피크 값은 최소와 최대 타이밍 오차의 차를 나타낸다.

TIE 지터는 유입되는 데이터 스트림에 따라 CDR(Clock and Data Recovery)의 PLL이 대응할 수 있는지 나타내기 위해 CDR PLL에서 중요하다. TIE 지터 값이 높으면, 유입되는 데이터 스트림의 변화에 CDR PLL이 적절히 대응하지 못한다는 뜻이다. 그림 2(c)에서 RMS TIE 지터 측정 값은 3.29ps, 피크 투 피크 측정 값은 27.93ps이다.

이 세 가지 지터 외에도, 위상 잡음(Phase Noise) 또한 클록 신호의 품질에 영향을 미친다. 위상 잡음은 주파수 도메인으로 측정하며, 신호 전력 대 잡음 전력의 비를 구하고 이것을 캐리어 신호로부터 특정 오프셋 지점에서 1Hz 대역폭으로 정규화하여 계산할 수 있다.

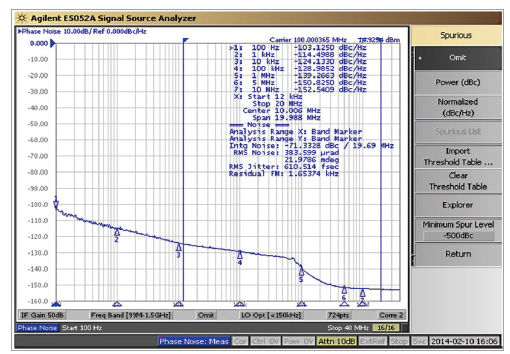

위상 지터(Phase Jitter)는 캐리어 신호부터 특정한 주파수 오프셋에 걸쳐 위상 잡음을 적분한 것이다(그림 3). 이 그림에서는 RMS 위상 지터 측정 값이 12kHz∼20MHz의 적분 범위에서 0.610ps라는 것을 알 수 있다.

위상 지터는 위상 잡음 플롯 하단의 면적을 적분하고 캐리어 신호의 에너지와 비교해, 캐리어 신호에서 특정한 주파수 오프셋에 걸쳐 존재하는 에너지의 양을 측정한 것이다. 예를 들어 SONET 네트워크 인터페이스는 위상 지터를 측정하기 위해 위상 잡음 플롯 하단 면적을 적분할 때 캐리어 신호로부터 12kHz∼20kHz의 주파수 오프셋을 이용한다. Fiber Channel 인터페이스는 위상 지터를 측정하기 위해 위상 잡음 플롯 하단 면적을 적분 시 캐리어 신호로부터 637kHz∼10MHz의 주파수 오프셋을 이용한다.

시스템 통합

그림 3. 이 위상 잡음 플롯은 주파수 도메인으로 잡음을 측정하며, 신호 전력 대 잡음 전력의 비를 구하고 이것을 캐리어

신호로부터 특정한 오프셋 지점에서 1Hz 대역폭으로 정규화하여 계산한다

그러므로 다수의 칩을 포함한 시스템 보드를 설계할 때는 아마도 대부분 다음과 같은 의사결정 단계를 따라야 할 것이다.

① 얼마나 많은 수의 클록 주파수를 필요로 하는지 결정한다.

② 보드에 있는 주요 칩들의 타이밍 마진을 분석하고 계산한다.

③ 업체 각각의 클록 생성 솔루션으로 어떤 것들이 있는지 알아보고 지터, 프로그래머블 특성, 전력 소모, 그 밖의 요인들을 평가한다.

④ 클록 신호 품질에 영향을 미칠 수 있는 누화와 기타 요인들을 방지하도록 클록 경로에 주의하여 회로 보드를 레이아웃한다.

⑤ 출력 I/O 레벨, 주파수, 기타 측면들을 조정해서 시스템 애플리케이션에 적합하게 클록 칩을 프로그램한다.

다중 출력 클록 제너레이터는 여러 업체의 제품을 이용할 수 있으므로, 어느 업체의 어느 제품을 이용할 것인지 선택하기 위해서는 칩 기능을 검토해 보고 그러한 기능들이 의도하는 애플리케이션에 적합한지 살펴보아야 한다.

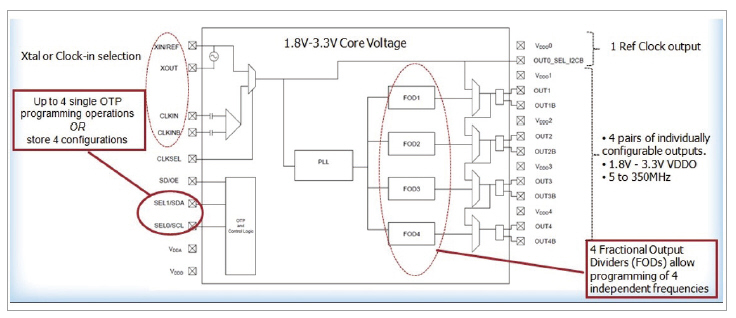

최신 기술의 역량을 보여주는 예로서, IDT의 저전력 프로그래머블 클록 제너레이터 제품군인 VersaClock 5 시리즈의 첫 번째 제품 ‘IDT5P49V5901’은 매우 우수한 지터 성능을 제공하며(0.7ps RMS 위상 지터, 정격), 3.3V일 때 100mW 미만의 코어 전력 소모를 달성한다(그림 4). 이와 같이 지터가 낮으므로 PCIe Gen 1/2/3, USB 3.0, 1/10기가비트 이더넷의 클로킹 요구를 충족한다.

그림 4. 개별 구성이 가능한 네 개의 차동 클록 출력을 제공하는 5P49V5901 VersaClock 5 클록 제너레이터는 우수한 지터 성능을 제공하며 350MHz의 입력 및 출력 주파수로 동작할 수 있다. 그리고 온칩으로 OTP 메모리를 포함하여 다중의 구성 패턴을 저장하고, 각각 다른 동작 모드로 이용할 수 있다

VersaClock 5 시리즈는 고성능 컨슈머, 네트워킹, 산업용, 컴퓨팅, 데이터 통신 애플리케이션에 이용하도록 설계되었으며, 최대 350MHz에 이르는 입력 또는 출력 주파수로 동작할 수 있다. 이들 칩 제품은 유연성이 뛰어나며 네 개의 개별적인 범용 차동 출력을 제공하므로 어떠한 출력 주파수라도 발생시킬 수 있고 LVPECL, LVDS, HCSL 또는 8개의 LV CMOS 출력으로 구성할 수 있다. 온칩 OTP(One-Time Programmable) 메모리를 포함하므로 네 개의 출력 각각에 대해 다중의 구성(클록 주파수, I/O 타입, 기타 설정)을 저장할 수 있다.

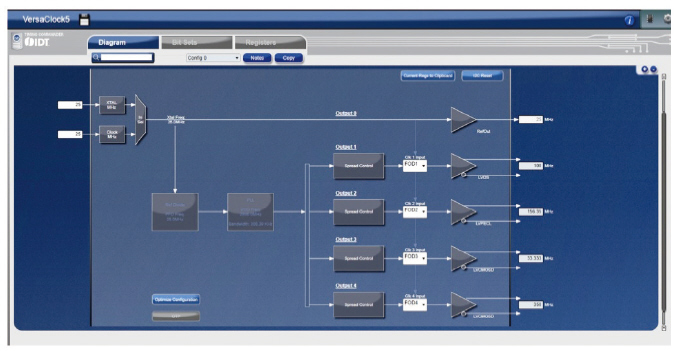

그림 5. VersaClock 클록 제너레이터를 프로그래밍하고 구성하는 작업을 간소화하는 툴이며, 그래픽 사용자 인터페이스를

이용하여 모든 파라미터를 설정할 수 있고 모든 I/O 핀을 구성할 수 있다

선택 핀 두 개를 제공하므로 최대 네 개의 구성 패턴을 프로그램할 수 있고, 프로세서 GPIO나 부트스트래핑을 이용하여 액세스할 수 있다(하나의 구성 패턴은 네 개의 클록 출력 포트에 대한 프로그래밍 데이터를 포함하고 있다). 네 개의 각각 다른 구성 옵션을 각각 다른 동작 모드에 이용하거나(완전 기능, 부분 기능, 부분 파워 다운 등), 각 지역 표준에 이용할 수 있으며(미국, 일본, 유럽 등), 시스템 생산 마진 테스트에도 이용할 수 있다. 이 칩은 또한 두 개의 I2C 주소 중 하나를 이용하도록 구성할 수 있으므로, 하나의 시스템 내에서 복수로 이용할 수 있다.

또한 별도의 I2C 직렬 포트를 칩으로 제공하므로 디자이너가 미리 저장된 설정을 오버라이드하거나, 테스트 시퀀스를 실시하기 위해 구성 레지스터로 새로운 구성을 로드할 수 있다. 각 출력의 주파수를 단일 레퍼런스 클록 또는 크리스털 입력을 이용하여 발생시킨다. 뿐만 아니라 매끄러운 수동 전환 기능은 정상 동작 중에 중복적인 클록 입력 중 하나를 선택할 수 있다.

IDT의 VersaClock 5 시리즈 같은 칩은 다중의 프로그래머블 기능들을 구성하는 작업이 까다로울 수 있다. IDT는 이러한 작업을 간소화할 수 있도록 Timing CommanderTM라는 툴을 제공하고 있다. 이 툴은 디자이너가 직관적이고 유연한 그래픽 사용자 인터페이스(GUI)를 이용하여 VersaClock 5 칩을 구성하고 프로그램할 수 있는 소프트웨어 플랫폼이다(그림 5).

Baljit Chandhoke / Integrated Device Technology Inc.