연산 집약적 맞춤 머신비전을 위한 아키텍처

머신비전 알고리즘 중 대부분은 연산 집약적이어서 전용 하드웨어를 필요로 한다. 하지만 매우 특수화된 카메라를 개발해야 할 경우에는 특수한 조건을 충족시켜주는 아키텍처가 요구된다. 이러한 유형의 조건을 가진 설계 중에 TI의 디자인 네트워크 회원사인 크리티컬 링크는 uPP 인터페이스 사용을 포함하는 TI OMAP-L138 DSP+ARM9 프로세서의 전원 및 유연성과 함께 자일링스의 FPGA 스파르탄-6을 활용하고 있다.

머신비전(Machine Vision) 기술 도입의 확대에 따라, 이 기술은 앞으로 다양한 애플리케이션에서 활용이 가능하다. 여기에는 시트 제품, 약품, 반도체, 면도날, 자동차 등 다양한 범주의 제품 제조에 필요한 장치와 검사장비가 포함된다. 머신비전의 애플리케이션은 종종 사전에 설정된 디바이스가 제공하지 않는 일련의 독특한 비전 시스템 요건을 갖춰야 한다.

이 글은 아키텍처와 추가적인 리소스를 자세히 설명하여 독자가 해당 아키텍처를 포함한 유사한 아키텍처를 바탕으로 각자의 비전 시스템 설계에 착수할 수 있도록 머신비전 시스템의 특정 클래스(연산 집약적인 머신비전 시스템)를 다룬다.

문제의 기술

머신비전 시스템 알고리즘 중 대부분은 매우 연산 집약적이어서 전용 하드웨어를 필요로 한다. 각 애플리케이션에는 비전 분석과 CODEC 또는 ASIC을 통한 영상 압축과 같은 전용 고정함수 디바이스 또는 코어보다는 DSP 또는 FPGA와 같은 프로그래머블 아키텍처에 적합하게 만드는 독특한 요건이 따른다.

현재 시장에 출시된 다수의 비전 제품은 표준 기반 비전 시스템에 적합한 빌딩 블록을 제공한다. 여기에는 OpenCV의 오픈소스 비전 알고리즘이 포함된다. 많은 비전 시스템이 지원해야 하는 표준은 몇 가지 상이한 표준 비디오 포맷(MPEG-4, H.264 등)을 사용하는 영상 인코딩 또는 트랜스코딩과 디지털 인터페이스(USB, GigE, Camera Link, HDMI 등)의 기본 세트 등이 있다.

하지만 매우 특수화된 카메라를 개발해야 한다면 어떨까? 초당 30프레임(fps) 또는 60프레임에서의 최고 해상도와 고선명도를 지원하는 카메라가 목표가 아니라, 작은 부분을 매우 높은 프레임 속도, 수천 프레임과 50×50 픽셀 해상도로 처리하는 완전히 맞춤화된 알고리즘을 요구할 수 있다.

반대로, 표준에서 벗어난 해상도가 매우 높은 이미지에 대한 맞춤 알고리즘을 보다 낮은 프레임 속도로 전력소비를 낮은 수준으로 제한하며 실행해야 할 수도 있다. 그리고 이러한 특수 카메라는 특수화된 ASIC의 개발에 필요한 일정, 비용 또는 리스크를 정당화하기에는 부족한 저·중 수준의 용량만을 필요로 한다.

이 글에서는 이와 같이 특수한 조건을 충족시켜주는 아키텍처를 소개하고, 설명한 개념을 바탕으로 독자가 자신의 설계를 발전시켜 나가는 데 필요한 리소스를 제공한다.

아키텍처

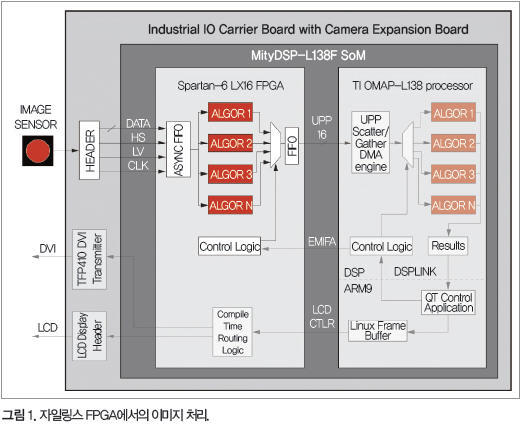

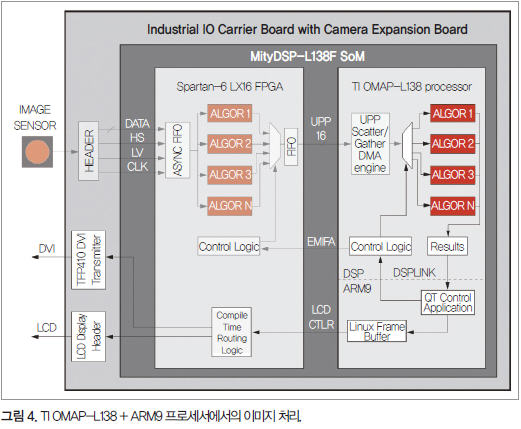

이러한 유형의 조건을 가진 몇 가지 설계 중에서 TI의 디자인 네트워크의 회원사인 크리티컬 링크(Critical Link)가 사용하는 아키텍처는 uPP 인터페이스 사용을 포함하는 TI OMAP-L138 DSP+ARM9 프로세서의 전원 및 유연성과 함께 자일링스의 FPGA 스파르탄-6을 활용하고 있다.

1. 자일링스 스파르탄-6과 프로그래밍 가능한 로직

하드웨어 설계에 프로그래머블 로직을 통합하면 시스템의 전반적 유연성이 상승한다. 이러한 경우, TI OMAP-L138 프로세서와 이 글에서 다루는 유형의 시스템에는 자일링스의 스파르탄-6이 적합한 선택이다. 스파르탄-6은 LVDS, LVTTL, LVCMOS 등의 다양한 시그널링 표준을 지원하도록 설정할 수 있는 SelectIO를 탑재하고 있으며, 설계하는 시스템에 가장 적합한 디지털 이미징 센서에 직접 인터페이스 하도록 맞춤화할 수 있다. 또한, FPGA와 센서 사이에 ADC를 설계함으로써 CCD 이미저와 같은 아날로그 기반 센서에 인터페이스 하기 위해 사용할 수도 있다.

FPGA를 통해 이미지 데이터를 획득한 후에는 프로그래머블 로직을 사용하여 데이터에 대한 다양한 작업을 신속하고 효율적으로 수행할 수 있다. FPGA는 에지(edge) 검출 또는 코너 검출, 추출 및 로우 레벨 분석 작업 등에 매우 적합하며 기본적인 프레임 투 프레임(frame-to-frame) 작업 또한 FPGA에서 효과적으로 수행할 수 있다.

FPGA의 또 다른 장점은 로우(raw) 데이터를 DSP/애플리케이션 프로세서가 처리해야 하는 데이터로만 추출할 수 있다는 것이다. 이는 최고 해상도 비디오 스트림의 모든 프레임을 높은 프레임 속도로 분석해야 하거나 데이터의 용량이 프로세서의 디지털 인터페이스가 수용할 수 있는 한계를 초과하는 등 DSP/애플리케이션 프로세서가 처리할 수 있는 수준 이상의 프로세싱 요건이 주어진 경우에 특히 유용하다. 애플리케이션 프로세서(예를 들면, 라이선스 플레이트(license plate) 또는 페이스(face))가 원하는 이미지의 특정 부분을 통계적 또는 역학적으로 식별하기 위해 FPGA를 사용하거나, 또는 이미지에 대한 배경 측정 또는 히스토그램과 같은 주요 통계적 데이터를 계산하고 이러한 정보를 OMAP-L138 프로세서 제공에 FPGA를 활용하면 로우 데이터를 추출할 수 있다.

자일링스의 스파르탄-6 FPGA는 매우 높은 프레임 속도로 데이터를 캡처하고 불필요한 프레임을 완전히 또는 부분적으로 제거할 수 있다. 그 후에는 관련 있는 데이터만을 DSP에서의 처리를 위해 전달하여 FPGA와 DSP/애플리케이션 프로세서 사이에 필요한 전반적인 대역폭을 줄일 수 있다.

자일링스의 스파르탄-6은 병렬 하드웨어 아키텍처를 사용하는 고성능 비디오 가속 블록을 실행할 때 사용할 수 있는 DSP48A1 슬라이스를 최대 180개까지 제공하며, 개발시간을 단축시켜 주는 비디오와 이미지 프로세싱 IP 코어 또한 제공한다.

마지막으로 자일링스의 FPGA는 비표준 인터페이스의 실행에도 사용될 수 있다. 이는 다중 디스플레이 또는 다중 카메라 시스템, 맞춤 동기식 직렬 인터페이스, 맞춤 병렬 인터페이스 또는 시스템 내부의 애플리케이션 프로세서가 지원하지 않는 추가적인 표준 인터페이스를 위해 더해진 기능일 수 있다. 이러한 인터페이스는 또다시 FPGA(LVDS 등)가 제공하는 다양한 물리적 레이어를 이용할 수 있다.

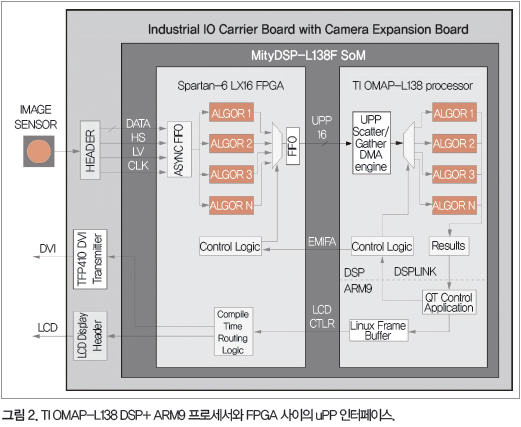

2, uPP를 통해 FPGA로부터 DSP로 이미지 데이터 전송

크리티컬 링크는 TI OMAP-L138 프로세서에서 uPP 인터페이스를 이용하여 자일링스의 스파르탄-6으로부터 OMAP-L138 프로세서에 장착된 DSP로 이미지 데이터를 전송한다. 이러한 인터페이스는 프로세서의 메모리로, 또는 메모리로부터 대용량의 데이터를 지속적으로 옮기기 위해 특별히 설계되었다.

uPP는 클록 사이클당 하나의 데이터 단어(8 또는 16bit)를 클록할 수 있다(또는 더블 데이터 레이트 [DDR]로 클록 사이클당 두 개의 데이터 단어를 처리할 수 있으나, 이러한 경우 클록 속도는 반으로 떨어진다). 최대 uPP 클록이 75MHz일 때 uPP의 클록 속도는 프로세서 최고 클록 속도의 50%이고 최대 스루풋은 150MBytes/s이다. 이렇게 간단한 uPP 인터페이스를 통해 FPGA와 쉽게 통합할 수 있다(그림 2 참조).

TI OMAP-L138 프로세서는 각각을 개별적으로 설정할 수 있는 두 개의 uPP 인터페이스를 포함한다. 하드웨어의 관점에서 uPP 인터페이스는 상당히 단순한 동기식 데이터 인터페이스로서 유효한 데이터와 시작/대기 조건을 표시해주는 몇 개의 컨트롤 핀과, 클록 핀, 데이터 핀으로 구성된다. 이러한 인터페이스는 별도의 연결 장치 없이 일부 병렬 ADC 및 DAC와 함께 사용할 수 있다.

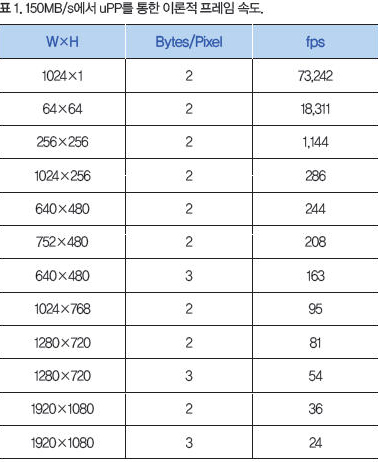

앞서 말한 uPP 데이터 속도를 예로 들자면, 표 1은 자일링스 스파르탄-6 FPGA에서 OMAP-L138 프로세서 시스템 메모리로 전송할 수 있는 이론상 최대 프레임을 보여준다. 이 표에 나타난 계산은 센서가 요구할 수 있는 인터 프레임(inter-frame) 갭 또는 인터 라인(inter-line) 갭을 고려하지 않았음을 기억해야 한다. 시스템을 확장할 때에는 데이터에 의도된 알고리즘을 수행하는 OMAP-L138 프로세서의 456MHz ARM9와 456MHZ 부동 소수점 DSP의 기능을 고려해야 하는데, 그 이유는 이것이 전반적으로 처리되는 프레임 속도에 영향을 미치기 때문이다.

이러한 작업은 프로토 타입 시스템 또는 평가 모듈에 의도된 알고리즘을 통해 실험해보면서 수행하는 것이 좋다. DSP 또는 ARM에서의 애플리케이션 처리가 시스템 설계의 제한적인 요소로 식별되는 경우, 이는 OMAP- L138 프로세서로부터 FPGA로 이동하는 반복적인 작업을 식별함으로써 FPGA를 최대한 활용할 수 있는 상황임을 의미한다. 따라서 DSP와 ARM은 비반복적인 작업, 더욱 글로벌한 작업 혹은 한 번에 다수의 프레임을 요구하는 작업에 사용할 수 있다. 캡처 속도가 매우 빠르고 uPP 주변장치가 로우 데이터의 전체 용량을 처리할 수 없을 때 FPGA를 사용하면 전체적인 데이터 속도를 줄일 수 있다.

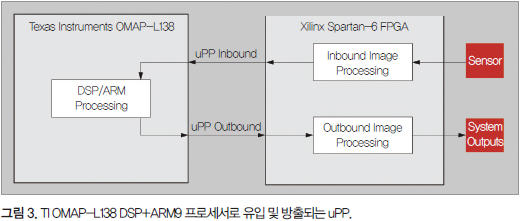

uPP의 두 가지 독립 채널을 사용하면 그림 3에 나타난 것과 같은 아키텍처를 편리하게 실행할 수 있다. 유입 데이터를 FPGA로 먼저 프로세싱한 후 uPP를 통해 OMAP-L138의 DSP로 보내 지능형 이미지/영상 분석 작업을 수행하게 할 수 있다. 또한, 데이터를 FPGA를 통해 출력 인터페이스로 돌려보낼 수도 있다. 데이터가 FPGA를 두 번째로 통과할 때 영상을 OMAP-L138의 ARM 코어가 제공하는 그래픽 사용자 인터페이스 위에 덮어씌우거나 OMAP-L138 프로세서가 지시한 대로 텍스트 또는 기타 그래픽 오버레이를 제공하는 등의 저수준 출력 프로세싱을 수행할 수 있다.

3. OMAP-L138 프로세서를 통한 통합 ARM과 DSP 프로세싱

지금까지 FPGA로의 데이터 획득, 데이터에 대한 FPGA 프로세싱, 이미지 데이터를 자체적으로 처리하기 위해 456MHz ARM9 애플리케이션 프로세싱 코어와 456MHz TMS 320C 674×DSP 코어를 통합하는 독특한 아키텍처를 제공하는 OMAP-L138 프로세서로의 데이터 전송에 관해 논의했다.

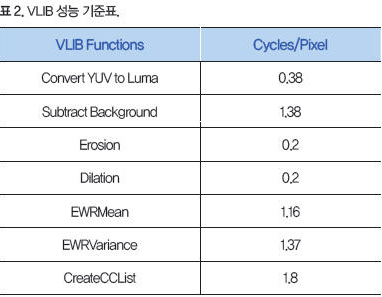

크리티컬 링크에서 OMAP-L138 프로세서와 자일링스 스파르탄-6 FPGA가 혼합된 아키텍처는 보통 OMAP-L138 프로세서의 DSP가 먼저 프로세싱된 이미지 데이터가 FPGA로부터 도착하면서 나머지 알고리즘 ‘헤비 리프팅(heavy lifting)’을 수행하도록 하면서 활용된다. CCS(Code Composer Studio) 통합 개발 환경(IDE)에서 TI가 제공하는 컴파일러를 사용하여 C 또는 C++에 수동 코딩되어 있으며 DSP에 최적화된 맞춤 알고리즘을 실행하거나, 또는 이미지 및 영상 처리를 위해 TI가 제공하는 최적화된 라이브러리(IMGLIB 와 VLIB)를 사용하면 이러한 작업을 수행할 수 있다. OpenCV는 DSP로 전송이 용이한 여러 가지 비전 관련 알고리즘을 지원하는 오픈 소스 라이브러리이다.

DSP는 객체 검출, 객체 식별, 에지 검출, 색상 전환, 이미지 필터링, 객체 추적, 리사이징과 같은 연산 집약적인 이미지 분석과 프로세싱 작업을 처리할 수 있다.

머신비전 알고리즘은 객체의 형태, 균열, 이물질 및 기타 이상을 찾아내기 위해 여러 가지 필터링 작업을 필요로 한다. 딜레이션(Dilation), 이로전(erosion), 해리스(Harris), 호(Hough), 하(Haar), 크래스피어(classfier)가 객체 검출과 기능 추출에 도움이 된다. 주로 루카스 카나데(Lucas Kanade), 광류(optical flow), 칼만(Kalman) 필터, 바타차리아(Bhattacharya) 거리, 가우시안(Gaussian) 모델이 객체 검출과 추적 알고리즘을 지원한다.

대부분의 이미지 처리 작업은 그레이 스케일 또는 RGB 컬러 모드에서 이루어진다. 캡처된 이미지 데이터가 YCbCR 포맷이라면 그레이 스케일 처리를 위해 휘도(luminance) Y 데이터를 사용할 수 있다. 필요한 처리의 유형에 따라 RGB 포맷으로 캡처된 데이터를 YCbCr 포맷으로 전환할 수도 있고, RGB 포맷으로 유지할 수도 있다. 광범위한 신호 처리 알고리즘을 수행하는 기능은 IMGLIB 또는 VLIB의 일부이거나 OpenCV에서 이용 가능한 기능이다. 개발된 애플리케이션은 외장 메모리로의 DMA 접근을 활용하여 보다 빠른 처리를 위해 데이터가 내장 메모리로 전송될 수 있도록 한다.

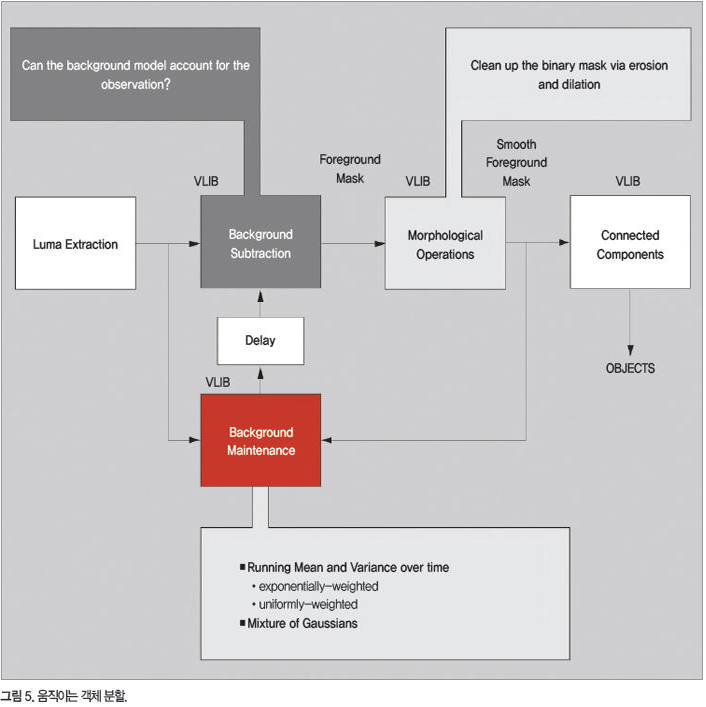

움직이는 객체 분할은 배경을 지우고 전경 데이터를 처리하면서 그레이 스케일 모드로 영상을 처리해야 하는 머신비전 처리의 사례이며, 전경 마스크에 대한 딜레이션과 이로전 등의 형태학적 작업을 통해 이루어진다. 객체의 경계는 연결된 부품 모델을 사용하여 형성된다(그림 5 참조).

16bit 정밀도의 움직이는 객체 분할은 단일 가우시안 모델의 16bit 정밀도보다 낮은 성능을 보인다. 필요한 작업의 유형에 따라 DSP에 공급되는 대략의 해상도를 선택할 수 있다. 데이터가 외장 메모리에 위치하고 있는 경우 VLIB 처리에 대한 50%의 추가적 오버헤드가 발생할 것이다.

외장 시스템 인터페이스는 ARM에 연결되고 ARM에 의해 관리되기 때문에 데이터 처리와 드라이버의 프로세싱 부하도 ARM에서 처리할 수 있다. 세 개의 이용 가능한 코어에 연산을 신중하게 분할함으로써 아키텍처로부터 최대의 프로세싱 파워를 이끌어낼 수 있다.

DSP 알고리즘 작업이 수행되면서 DSP는 OMAP-L138 프로세서에서 ARM과 소통하고 ARM을 통해 외부 세계와 정보를 주고받을 수 있다. 이는 로컬 사용자 인터페이스 또는 원격 사용자 인터페이스일 수 있고, 보다 큰 시스템 내부의 또 다른 하위 프로세싱 시스템일 수도 있다. DSP는 공유된 메모리, 메일함 또는 TI의 DSPLink 라이브러리가 제공하는 다양한 기타 메커니즘을 통해 ARM과 소통할 수 있다. RingIO, MessageQ, Notify가 DSPLink 내부에서 이러한 소통을 위한 인터페이스를 제공한다. ARM과 DSP 사이의 공유 메모리 구역은 이러한 프로세서들 사이에서 데이터 포인터를 공유하기 위해 사용되며 DSPLink 라이브러리는 데이터 교환의 효율성을 증진시킨다.

구성 데이터는 ARM으로부터 DSP로 전달될 수 있으며 측정, 통계, 로우 미이지/영상 데이터 또는 처리된 이미지/영상 데이터는 외부 세계와의 공유를 위해 ARM으로 전달될 수 있다. ARM은 임베디드 리눅스, 윈도 CE, QNX 또는 쓰레드X와 같은 완전한 기능 운영체제를 실행할 수 있기 때문에 커뮤니케이션과 디스플레이 기능에 특히 적합하다.

요약

이 글은 머신비전 시장의 매우 다양한 요구조건 중 일부를 충족시키는 아키텍처에 대한 정보를 제공한다.

이러한 아키텍처는 자일링스의 스파르탄-6 FPGA(설계에 기타 FPGA 제품군도 사용할 수 있다), TI OMAP- L138 프로세서가 제공하는 부동 및 고정 소수점 DSP 및 ARM9, 그리고 사용하기 쉬운 uPP 인터페이스 주변장치를 활용한다.

아래의 ‘유용한 링크’에서 이러한 각각의 문제에 대한 더 자세한 정보를 얻을 수 있을 것이다.

· 크리티컬 링크 MityDSP (www.mitydsp.com)

· 크리티컬 링크 비전 개발 키트 (www.mitydsp.com/products-services/base-boards/vision-dev-kit)

· TI OMAPL138 DSP+ARM9 processor (www.ti.com/product/omap-l138)

· 자일링스 Spartan6 (www.xilinx.com/products/silicon-devices/fpga/spartan-6/index.htm)

· 자일링스 이미지 처리 라이브러리 (www.xilinx.com/products/intellectual-property/EF-DI-VID-IMG-IP-PACK.htm)

· TI IMGLIB (www.ti.com/tool/sprc264)

· TI VLIB (http://processors.wiki.ti.com)

· TI CCS IDE (www.ti.com/tool/ccstudio)

· 오픈소스 OpenCV (http://opencv.org)

· TI의 OpenCV (www.ti.com/litv/pdf/spry175)

XMRGL 크리티컬 링크의 비전 개발 키트와 MityDSP-L138F SoM은 자신의 설계에서 이러한 아키텍처를 자세히 탐구할 수 있는 편리한 플랫폼을 제공한다.

아시 바르드와지 텍사스 인스트루먼트 DSP 선임 애플리케이션 엔지니어