테크노트 프로그래머블 다중 출력 클록 제너레이터 IC로 시스템 클로킹 간소화

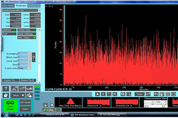

클로킹 요구가 다른 통합 칩들을 포함한 시스템 보드를 설계할 경우, 설계상 각각의 타이밍 요구를 이해하는 것이 중요하다. 디자이너들은 칩으로 지터와 클록 주기를 비롯, 다양한 타이밍 제약을 충족하는 클록 신호를 제공해야 한다. 다중의 프로그래머블 출력을 지원하는 최신 프로그래머블 클록 제너레이터를 이용하면 다양 한 시스템 타이밍 요구를 충족할 수 있으며, 향후 시스템 발전에 따른 성능 요구에도 대응할 수 있다. 오늘날 복잡한 시스템 보드는 애플리케이션 프로세서, 고성능 범용 프로세서, 다중의 시스템온칩(System-on-a-Chip)을 포함하고 있다. 이러한 고성능 회로들은 애초에 함께 작동할 것을 고려하여 설계된 것이 아니므로 각각 클록 주파수 요구가 다를 수 있다. 뿐만 아니라 보드 상의 회로들은 각각 클록 안정성(지터)과 클록 주기 비율(듀티 사이클)을 비롯한 타이밍 제약이 다를 수 있다. 그림 1. 셋톱박스의 블록 다이어그램 (클록 주파수와 클록 안정성 요구가 각각 다른 다수의 회로 기능들을 포함하고 있다. 통상적으로는 다수의 타이밍 신호를 제공하기 위해 다중의 클록 오실레이터를 이용한다) 따라서 이와 같이 복잡한 보드에서는 각각 칩들에