두께 조절할 수 있는 단결정형태 질화붕소 합성 기술 최초 개발 수소연료전지 전해질막, 차세대 이차전지 전극, 양자광원 등 응용 가능 UNIST·영국 케임브리지 대학교 공동연구팀이 차세대 고집적 반도체에 들어갈 2차원 절연체 소재 합성 기술을 개발했다. 과학 저널 Nature지에 공개된 해당 기술은 2년마다 반도체 칩의 미세소자 집적도가 2배씩 증가한다는 ‘무어의 법칙’의 물리적 한계를 극복할 기술로 주목받고 있다. 고집적 반도체 칩의 전류누설과 발열과 같은 한계를 해결하기 위해 실리콘을 나노공정으로 얇게 깎는 대신, 이를 얇은 2차원 반도체 소재인 이황화몰리브덴 등으로 바꾸는 반도체 칩 기술이 대안으로 꼽히고 있다. 하지만 이 기술을 완성하기 위해서는 칩 성능을 떨어뜨리는 전하 트랩과 전하 산란을 막을 2차원 절연체 소재 또한 꼭 필요하다. 공동 연구팀은 2차원 소재 중 유일한 절연체인 질화붕소를 원자 세 층 두께의 단결정 형태로 합성할 수 있는 기술을 세계 최초로 개발했다. 질화붕소가 두꺼울수록 절연체로 쓰기 적합한데, 그간 두께를 조절할 수 있는 합성 기술 개발이 난제로 남아 있었다. 제1 저자인 마경열 연구원은 “상용화가 가능한 큰 크기의 육방정계 질화

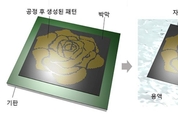

헬로티 김진희 기자 | 반도체 메모리의 용량이 1년마다 두 배씩 증가한다는 ‘황의 법칙’, 반도체 집적회로의 성능이 2년마다 두 배씩 증가한다는 ‘무어의 법칙’이 있다. 그러나 최근에는 기술 개발의 한계로 반도체 성능을 높이는 데 어려움이 따랐다. 이 가운데 국내 연구팀이 고순도 소재 박막 양면을 모두 반도체 소자로 만들 수 있는 기술을 개발했다. 개발된 기술을 활용하면 반도체 성능을 획기적으로 향상시킬 수 있다. 포스텍 기계공학과 김석 교수 연구팀은 미국 일리노이대 어바나-샴페인캠퍼스와 버지니아대와의 공동연구를 통해 자체적으로 박리되는 고순도 실리콘 박막을 기판 위에 옮기는 전사 기술을 개발했다. 연구에서 박막, 기판, 그리고 이들이 담긴 용액의 표면 물성을 고려해 조합한 결과, 건조한 상태에서 기판에 강하게 붙어있던 박막이 용액 안에서 자체적으로 떨어져 나갔다. 김석 교수팀은 박막을 앞면이 위로 향하게 기판 위에 전사한 뒤 반도체 공정 후, 용액 안에 넣고 자체 박리된 박막을 뒤집었다. 뒤집힌 박막을 용액에서 꺼내 다시 공정 기판에 뒷면이 위로 향하게 전사함으로써 양면에 반도체 공정을 할 수 있었다. 이 연구성과를 활용하면 실리콘 뿐만 아니라 GaN(질화

[첨단 헬로티] ▷▶이보 볼젠(Ivo Bolsens) 자일링스 수석 부사장 겸 CTO(Chief Technology Officer) 이미 여러 차례 무어의 법칙(Moore’s Law)에 대한 종말이 선포된 것을 고려하면, 우리는 지금 포스트-무어의 시대에 살고 있다고 말하는 것이 적절할 것이다. 그렇지만 어느 누구도 발전의 속도를 늦추려고 하지는 않을 것이다. 트랜지스터 밀도에 대한 고든 무어(Gordon Moore)의 관점은 커즈와일(Kurzweil)이 언급한 수확가속의 법칙(Law of Accelerating Returns)에서처럼 기본 기술의 장기적 흐름을 보여주는 한 측면에 불과하다. 무어의 시대에 기업들은 새로운 프로세스 노드가 가져다 주는 이익에 만족하고, 다소 안주한 경향이 있었던 것도 사실이다. 비록 속도는 느리지만, 확장은 계속될 것이며, 또한 무어의 법칙이 더 이상 효력을 발휘하지 않게 됨에 따라 새로운 트렌드를 보다 강하게 추진할 수 있는 동기가 부여되고 있다. ▲이보 볼젠(Ivo Bolsens) 자일링스 수석 부사장 겸 CTO(Chief Technology Officer) 최근에는 멀티칩 3D 통합과 같은 몇 가지 흥미로운 새