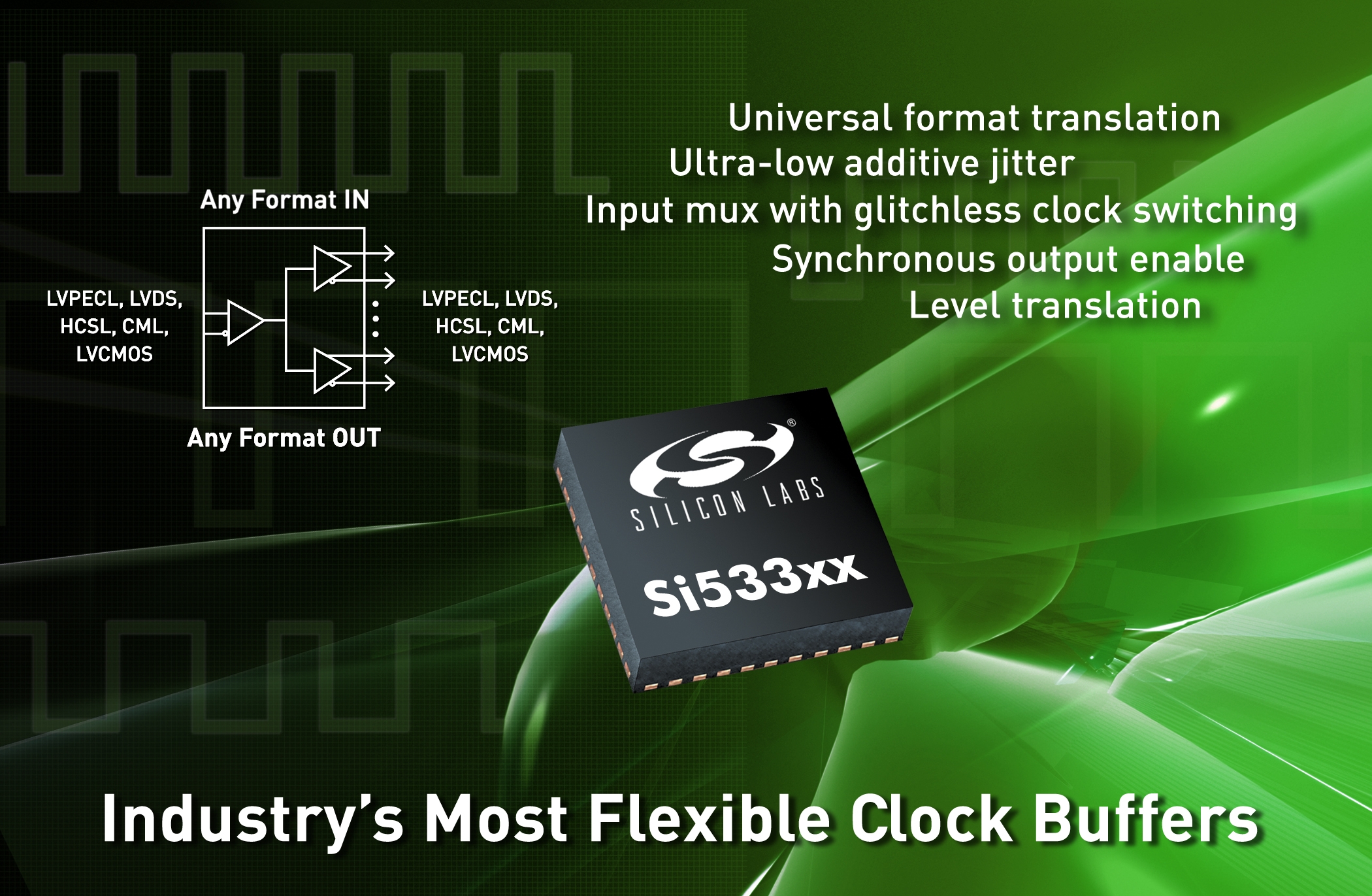

실리콘 래버러토리스는 LVPECL, LVDS, CML, HCSL, LVCMOS 버퍼를 단일 IC로 대체할 수 있는 범용 클록 버퍼 제품군(제품명: Si533xx)을 업계 최초로 출시하여, 정해진 포맷의 다수의 버퍼를 사용할 필요가 없다고 발표했다.

Si533xx 제품군은 클록 분배, 클록 다중화, 클록 분주, 포맷 및 레벨 변환 등 일반적인 클록 트리 기능들을 통합했다. Si533xx 제품군은 특허된 저 페이즈 노이즈(low-phase-noise) 클록 드라이버 아키텍처를 기반으로 하여, 최대 지터 스펙을 보장하는 극히 낮은 가산 지터(Additive Jitter)를 제공한다. 이에 따라 클록 트리 설계가 간소화되고 다른 디바이스에 대해 더 많은 지터 마진을 설계자에게 제공한다. Si533xx 클록 버퍼는 통신, 데이터센터, 무선 인프라, 방송 비디오 및 임베디드 컴퓨팅 애플리케이션 등 까다로운 요구 조건을 충족시키기 위한 목적으로 개발되었다.

Si533xx 클록 버퍼 제품군은 실리콘랩스의 포괄적인 타이밍 디바이스 포트폴리오 가운데 하나이다. 이 제품군을 통해 고객들은 어떠한 고성능 애플리케이션에도 알맞은 완벽한 클록 트리 솔루션의 설계와 구매를 단순화게 처리할 수 있다. 실리콘랩스 기반의 클록 트리는 업계 최고 수준의 통합을 제공하여 클록 생성과 배포에 필요한 컴포넌트의 수를 최소화한다. 단일 공급업체로부터 모든 타이밍 컴포넌트들을 조달할 수 있게 되어, 고객의 공급망을 단순화 하면서도 엔드-투-엔드 성능이 보장되고 상호 운용성의 문제를 해결할 수 있다.

경쟁 클록 버퍼들은 하나의 출력 신호 포맷만을 지원하고 기본적인 클록 트리 기능은 통합하지 않고 있다. 이러한 결함으로 설계자는 자신들의 클록 배포에 필요한 요구사항을 맞추기 위해 여러 디스크리트 버퍼, 다중화기, 분주기, 레벨 변환기를사용할 수 밖에 없어 설계 복잡성과 비용이 증가한다. 실리콘랩스의 유연하고도 고도로 통합된 솔루션은 이러한 문제를 해결하여 유연성을 높이고 클록 트리는 간소화하며 설계 복잡성은 낮추고 구매에 따른 문제점은 없애준다.

Si533xx 클록 버퍼는 최대 10개의 출력으로 격차 LVPECL, LVDS, CML 및 HCSL 버퍼를 대체하고 최대 20개의 출력으로 LVCMOS를 대체하며, 다중화기, 분주기, 레벨 변환기를 대체하는 단일 칩 솔루션으로 제공된다. Si533xx 클록 버퍼의 이러한 독창적인 아키텍처는 설계 유연성을 극대화한다. 클록 출력은 두 개의 독립적인 뱅크로 나누어져 있다. 각각의 뱅크 신호 포맷은 간단한 핀 스트래핑(pin-strapping)을 통해 사용자가 선택할 수 있어 개발자들에게 다양한 옵션을 제공한다. 두 개의 뱅크 모두 코어 전압과는 독립적인 전압 공급 핀이 할당되어 간단한 전압 레벨 변환이 가능하다. 이 제품의 범용 입력단은 두 개의 디퍼렌셜 혹은 싱글 엔드의 입력을 허용하고 저잡음 2:1 입력 다중화는 매끄러운 스위칭을 지원하여 입력 클록 스위칭 동안 런트 펄스(runt pulses)가 기기의 출력에 전달되는 위험을 없애준다. 또한 일부 Si533xx 버퍼들은 각각의 출력 클록의 출력이 활성화될 수 있도록 하는 개별 제어를 지원하여 컨트롤 유연성을 제공한다.

Si533xx 제품군은 성능을 저하시키지 않고도 높은 수준의 통합과 유연성을 제공할 수 있도록 설계되었다. Si53302 디바이스는 업계 최저 지터 다중 포맷 버퍼(통상100 fs RMS )로, 이미 포맷이 정해진 동종 최고의 버퍼와 견줄 수 있는 성능을 제공한다. 또한 이 제품의 2:1 입력 다중화기는 클록 입력 사이에 60dB 이상의 잡음격리를 제공하여 크로스톡에 의한 지터를 최소화하고 두 개의 입력 클록을 요구하는 애플리케이션에서의 저잡음 동작을 보장한다. 온칩 전압 정류기는 FPGA, ASIC, SoC 및 PHY에 있어, 높은 PSRR(power supply noise rejection)을 제공하면서 낮은 지터의 강건한 동작을 보장한다.