매스웍스(MathWorks)는 한국전자통신연구원(ETRI)이 매트랩(MATLAB)과 시뮬링크(Simulink)를 활용해 직교형 레이다 신호 송수신용 실시간 신호처리 모듈을 개발했다고 25일 밝혔다. 이 모듈은 내셔널인스트루먼트(NI)의 FPGA(Field-Programmable Gate Array) 기반 레이다 에뮬레이션 동작을 가속화한다.

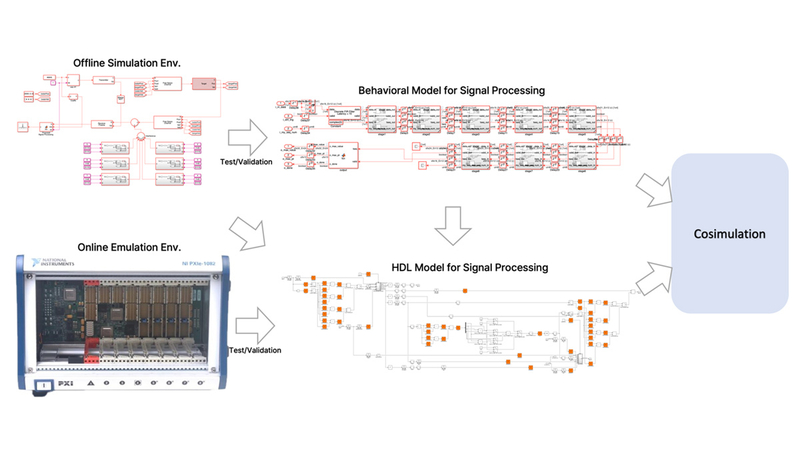

ETRI 전파연구본부는 소출력 레이다 시스템에서 직교형 레이다 신호 송수신을 처리하는 복잡한 과제를 해결하기 위해 모델 기반 설계(MBD)를 도입했다. 연구팀은 시스템 수준에서 알고리즘을 설계·검증한 뒤 자동으로 HDL 코드를 생성해 하드웨어에 구현하는 방식을 적용, FPGA 기반 실시간 처리 시스템의 개발 효율성과 정확도를 동시에 끌어올렸다.

연구 과정에서 CPU 기반 방식만으로는 다중 신호를 제때 처리하기 어려운 한계가 확인됐다. 특히 정합 필터 뱅크와 같은 병렬 처리 알고리즘은 실시간 실행이 요구됐고, 직교 신호 수신기는 파이프라인 구조로 구현돼야 했다. 이에 연구팀은 NI FPGA 전환을 선택했으나, 매트랩 알고리즘을 수동으로 HDL 코드로 옮기는 과정에서 비효율과 오류가 발생하는 문제가 있었다.

이를 해결하기 위해 연구팀은 시뮬링크 모델을 기반으로 HDL 코더(HDL Coder)를 통해 HDL 코드를 자동 생성하는 워크플로우를 구축했다. 이 과정에서 다양한 설계 옵션을 쉽게 평가할 수 있었고, HDL 베리파이어(HDL Verifier)를 활용해 알고리즘과 생성된 HDL 코드의 동작을 코시뮬레이션으로 비교 검증했다.

김형중 ETRI 책임연구원은 “매트랩 펑션 블록을 사용하면 주요 알고리즘 코드를 별도 수정 없이 그대로 적용할 수 있어 유용했다”며 “HDL 전문 지식이 없어도 HDL 코더를 통해 알고리즘을 HDL 코드로 쉽게 변환할 수 있었다”고 말했다.

ETRI는 이번 접근 방식을 통해 HDL 코드 구현 및 검증에 필요한 시간과 노력을 기존 대비 약 50% 줄였다. 또한 알고리즘 설계자와 하드웨어 엔지니어 간 워크플로우가 통합돼 반복 작업과 인적 오류도 감소했다. 연구원은 향후 머신러닝 기반 알고리즘을 포함한 프로젝트에서도 자동 HDL 코드 생성을 적극 활용할 방침이다.

정승혁 매스웍스코리아 애플리케이션 엔지니어는 “ETRI의 직교형 레이다 신호 개발에서 매트랩과 시뮬링크가 복잡한 알고리즘을 FPGA 하드웨어로 구현하는 데 핵심 역할을 했다”며 “앞으로도 한국 연구기관과 협력을 통해 차세대 기술 개발을 적극 지원하겠다”고 밝혔다.

헬로티 이창현 기자 |