AMD "5세대 AMD 에픽(EPYC) CPU에 대한 실리콘 구현 및 검증 완료"

AMD가 자사의 차세대 서버용 프로세서인 코드명 '베니스(Venice)'를 세계 최초로 TSMC의 2나노미터 공정 기술을 적용한 고성능 컴퓨팅(HPC) 반도체로 개발 중이라고 밝혔다. 이 제품은 내년 출시를 목표로 하며, AMD의 데이터 센터 CPU 로드맵에서 전략적 전환점을 상징하는 주요 제품으로 평가된다.

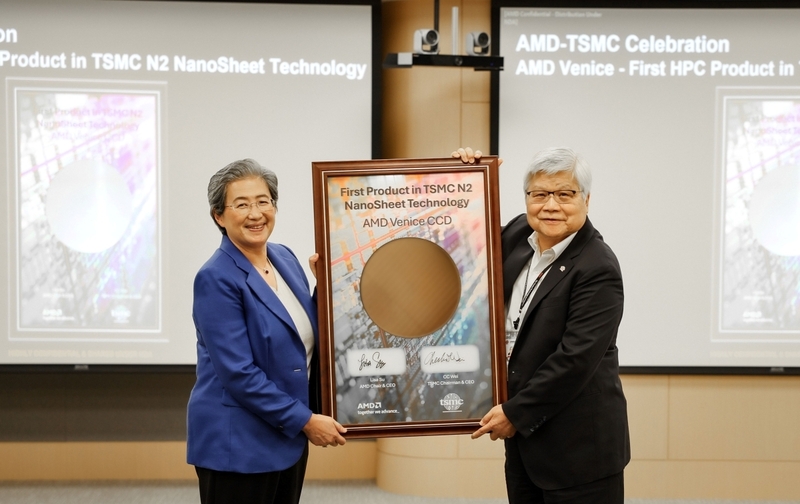

AMD는 이번 베니스 테이프아웃을 통해 TSMC와의 협업이 단순한 고객-공급자 관계를 넘어 고성능 반도체의 아키텍처 설계와 제조 공정 최적화를 동시에 실현하는 전략적 파트너십임을 강조했다. AMD는 이와 함께 TSMC의 미국 애리조나 신규 반도체 제조시설인 'Fab 21'에서 5세대 AMD 에픽(EPYC) CPU에 대한 실리콘 구현 및 검증을 성공적으로 완료했다고 전했다. 이는 미국 내 고성능 반도체 생산 역량을 확대하려는 움직임과도 맞물리며 주목받고 있다.

AMD 리사 수 CEO는 "TSMC는 AMD의 핵심 파트너로서 고성능 컴퓨팅(HPC) 한계를 확장해나가는 데 있어 매우 중요한 역할을 해 왔다"며, "이번 N2 공정 기반 제품 개발과 미국 내 팹 활용은 AMD가 기술 혁신과 미래 컴퓨팅을 실현하는 데 있어 지속적인 리더십을 유지하고 있음을 보여주는 결과"라고 밝혔다.

TSMC 웨이저자 회장 역시 이번 협력에 대해 환영의 뜻을 밝혔다. 그는 "AMD가 TSMC의 N2 공정과 애리조나 Fab 21의 HPC 주요 고객으로 자리한 것을 자랑스럽게 생각하며, 양사 협력을 통해 고성능 반도체의 성능과 전력 효율, 수율을 지속적으로 개선하고 있다"고 강조했다.

이번 발표는 TSMC가 본격 양산을 준비 중인 2나노 공정의 초기 성과를 보여주는 동시에 AMD가 AI, 클라우드, 고성능 서버 시장에서의 기술 주도권을 강화하고 있음을 의미한다. 특히 AMD의 차세대 에픽 CPU가 TSMC의 최신 기술력과 결합됨으로써 향후 서버 시장에서 인텔 및 다른 경쟁사와의 격차를 벌릴 수 있을 것으로 예상된다.

베니스는 AMD가 지난 수년간 쌓아온 고성능 CPU 설계 역량을 바탕으로, 정교하고 에너지 효율적인 데이터 센터용 솔루션을 제공하기 위한 핵심 프로젝트다. 이번 성과는 반도체 설계사와 파운드리 간의 협업이 단순한 기술 공급을 넘어, 제품 기획 초기 단계부터 공정 최적화를 반영한 공동 개발의 중요성을 부각시키는 사례로 해석된다.

헬로티 서재창 기자 |