제 2 장 기술개발 내용

제 1 절 당해년도 목표

(1) 기술개발 최종목표

■ 초다층 적층 및 레이저 에칭 기법을 이용한 고집적 인쇄회로 제조기술 개발

◦ 다층 bonding을 통한 고다층 lay-up 제조 기술 개발

◦ Chemical + Laser의 하이브리드 에칭을 이용한 미세 선폭 구현 기술 개발

(2) 1차년도 개발목표

■ 초다층 적층 및 레이저 에칭 기법을 이용한 고집적 인쇄회로 제조기술 개발

(Phase 1)

◦ 순차 bonding 적층 설계 및 engineering sample 제작 후 성능 평가

- 층간 오차 정밀도 < 50um

- 최대 적층 수 < 50

- 홀 간격 < 0.35mm

- 압착부 면적 < 30mm(w) 12mm(h)

◦ 레이저 식각 공정 셋업 및 패턴 형상 특성 평가

- 레이저 패턴 width < 50um

- 레이저 패턴 space < 60um

- 레이저 조사 에너지 < mJ

제 2 절 당해연도 개발 내용 및 개발 범위

(1) 순차 bonding시 가접 bonding 물성 평가 및 공정 설계

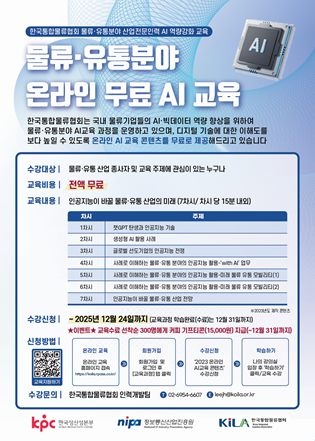

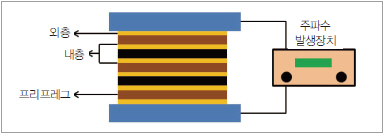

순차 bonding 공정을 위해선 인쇄전자회로기판 층 간의지지 역할을 할 수 있는 가접 bonding 이 필요함. 가접 bonding을 위해선 bonding 재료인 Pre-Preg(PP)의 물성 특성을 정확히 평가할 필요가 있다(그림 1).

▲ 그림 1

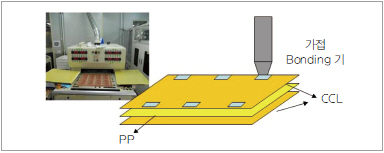

Pre-Preg는 열과 압력을 동시에 가하는 열압착 공정을 통해 완전 고체화되는 과정을 거쳐 상단 인쇄전자회로기판과 하단 인쇄전자회로기판을 물리적으로 결합시켜주는 역할을 한다. 이때 Pre-Preg에 가해주는 열, 압력, 시간의 공정 변수가 발생하게 되며, 정확한 물성 평가를 통해 신뢰성 있는 가접 bonding 결과를 도출할 수 있다. 그림2는 온도에 따른 고분자의 일반적인 물성변화를 나타내는 것으로, 고분자는 온도에 따라 완전 탄성체 (고체)에서 반유체 상태로 전이하는 특성을 나타내며, 이를 유리전이온도라고 함. 따라서 Pre-Preg의 유리전이온도를 관찰하면 최적의 가접 bonding 온도, 압력, 시간의 도출이 가능하다.

▲ 그림 2

또한 전체 접착력은 단위면적당 접착력을 접착부 면적의 곱인 까닭에, 접착 면적의 선정이 중요하다. 본 과제에서는 현재 인쇄전자회로기판 장치산업에서 일반적으로 구축된 기본 가접 면적인 30mm(w)X12mm(h)에서 원하는 접착력을 도출할 수 있도록 공정 설계를 진행하고자 하며, 2차년도에서는 공정 최적화를 통해 가접 면적 최소화를 진행하고자 한다.

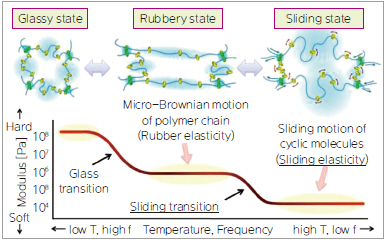

상기의 과정은 최적 제조 조건이 다수의 변수에 의해 결정되는 바, 수차례의 반복 실험이 필요하다. 따라서 명확한 실험 설계를 통해 최소 실험 조건을 도출하는 것이 중요하며, 따라서 아래와 같이 factorial design 기법을 도입하여 공정 변수 중요도와 적합값을 도출하고자 한다.

▲ 그림 3

(2) 레이저 식각 공정 셋업 및 패턴 형상 특성 평가

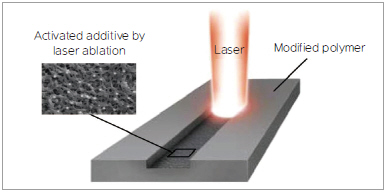

레이저 패터닝 기술은 미세 선폭 구현에 유리한 기술로서, 레이저의 강한 빛 에너지를 굉장히 좁은 면적으로 집광하여 순간적으로 물체를 태우는 원리다. 그림4처럼 집속된 빛에너지를 받은 물체의 분자 사슬이 끊어지게 되어 원 기판에서 분리되는 형태가 laser ablation (레이저 식각) 기술이다.

▲ 그림 4

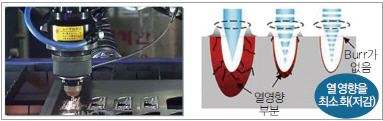

레이저 식각 기술을 이용해 미세선폭을 구현하기 위해선 우선 레이저 식각 시스템을 구축할 필요가 있다. 기존의 laser ablation 상용 기기들이 다수 판매되고 있으나, 대부분 CO2 gas laser로 본 과제에서 식각하고자 하는 인쇄전자회로기판 도체인 동(cupper)박 재료에 적합하지 않다. 따라서 인쇄전자회로기판 동박 식각에 적합하고 보다 유리한 레이저 식각 시스템을 평가 구축할 필요가 있으며, 크게 식각에 사용되는 레이저 소스와 광학계, 그리고 평가에 사용되는 이미징 시스템의 평가가 필요하다. 그림5처럼 좌측의 레이저 식각을 진행할 경우, 식각의 형태는 레이저 파장, 파워, 조사 시간, 기판 재질에 따라 우측과 같이 서로 다른 패터닝

▲ 그림 5

형상을 나타낸다. 이때, 도체의 잔사가 남지 않으면서 또한 기판의 열 데미지를 최소화한 형태로 패터닝하는 것이 매우 중요하다.

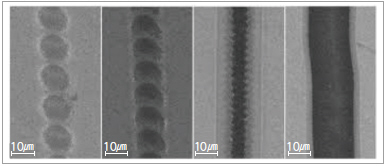

정교한 미세패터닝을 위해 레이저 조사 방법 (파장, 파워, 시간)에 따른 레이저 식각 패턴의 형상을 평가할 필요가 있다. 그림6처럼 레이저 식각을 진행할 경우, 좌측의 그림에서 보는 것과 같이 기판 중 레이저에 조사된 영역이 ablatoin되어 식각된다. 그러나 충분한 레이저 식각이 되지 않을 경우, 식각된 영역 사이에 기판 잔막 혹은 잔사가 남게 되어 short 불량이 발생하게 됨. 반대로, 레이저 조사량이 많을 경우 패턴의 일부가 소실되어 배선이 끊어지는 open 불량과 더불어 기판에 열 데미지 불량이 발생하게 된다. 따라서 1차년도에서는 인쇄전자회로기판 동박의 레이저 식각 기초 평가를 면밀히 수행하여, 미세 패턴용 레이저 식각 시스템을 구축함과 더불어 기존 chemical etching에 준하는 미세 패턴을 구현하고자 한다. 2차년도에서는 식각 공정 최적화를 통해 chemical ethcing 보다 우수한 미세 패터닝 기술을 개발하고자 한다.

▲ 그림 6

제 3 장 결과 및 향후 계획

제 1 절 연구개발 추진 체계

(1) 연구개발 추진 전략

고집적 인쇄전자회로기판 생산 제조 기술은 단일 요소 공정 기술로 불가능한 제품 목표다. 따라서 수직 축 (z)으로 공간을 확장하는 다층 인쇄전자회로기판 기술과 평면 축(xy) 상에서의 배선 밀도를 높이는 미세선폭 구현 기술이 동시에 개발되어야 한다. 기존 다층 적층 기술의 경우 층간 정밀도 불량 문제 및 적층 가능한 층수 제한의 근본적인 문제가 있었다. 따라서 본 과제에서는 신규 다층 적층 방식으로 순차 적층 bonding 기술을 구현하고자 하며, 이를 통해 70층 이상의 초다층 인쇄전자회로기판의 제조가 가능한 공정 기술을 확보하여 (주)스마트코리아에 기술 지원하고자 한다. 동시에 고집적 인쇄전자회로기판 구현 기술의 일환으로 배선 선폭의 밀도 향상이 가능한 미세선폭 기술을 구현하고자 한다. 이를 위해서, laser ablation을 이용한 레이저 식각 기술을 도입하고자 하며, 기존 장치산업에 사용되는 포토리소그래피 공정과의 융합을 통해 대면적 패터닝에 적용하고자 한다. 특히 각 공정의 핵심 변수를 도출 한 후, 이를 최적화하여 최고의 성능을 낼 수 있는 공정 기술을 지원하고자 함. 또한 현장 적용 시 발생하는 문제점을 실시간으로 면밀하게 파악하여 생산 마진이 높은, 즉 불량률이 최소화된 안정화된 공정이 될 수 있도록 할 예정이다. 이러한 과정을 통해 얻어진 공정 데이터를 표준화된 방법을 통해 계측하여 데이터베이스화를 진행할 계획이다. 이를 통해 표준 공정 사양표의 도출이 가능할 것으로 기대하며, 고사양/고신뢰성 반도체 검사용 특수 인쇄전자회로기판 제품의 국제적 신뢰성을 확보할 수 있도록 할 계획이다.

(2) 당해연도 연구개발 추진 실적

2-1. Ink-jet프린팅 공법을 이용한 레이져 소결 미세 패터닝 기술 개발

가. 서론

현대의 전자기기는 소형화, 경량화와 함께 고성능화, 복합화의 기능을 갖추는 방향으로 발전하고 있다. 소형화 에서도 어느 정도의 한계가 있기 마련인데, 조작을 할 수 없을 정도의 과도한 소형화는 불필요하다. 반대로 가정용 TV 등은 대화면에 수반하여 대형화되고 있다.

그러나, 경량화에 대한 요구에는 한계가 없다. 가벼우면 가벼울수록 장점이 많이 수반되며 특히 휴대기기의 경우에는 이러한 요구는 뚜렷하다. 그 외의 용도에서도 가벼워지면 충격을 받아도 고장의 발생이 줄어들고, 기구적으로도 컴팩트하게 할 수 있으므로 코스트 다운으로도 이어진다. 또, 소형화에 대해서도 장치 그 자체에는 각각 적당한 크기가 있지만, 회로부분은 소형화되면 그것을 넘는 일은 없다. 회로 부분이 작아지면 그 빈부분에 새로운 기능을 추가할 수 있기 때문이다.

또, 부품이나 회로가 작아지면 사용하는 재료도 적어지고, PCB도 작아진다. 이에 따라 코스트도 저하되고, 원재료의 절약, 장래에 장치를 폐기할 때 쓰레기의 경감 등 환경에 대해서도 유리하게 된다. 얼마나 회로를 가볍고 작게 할 것인가는 실장의 큰 테마이다.1)

이러한 전자기기의 개발성향에 따라 탑재되는 부품이 소형화 되었고 접속을 위한 핀 수도 급격히 증가하였다.2), 3) 특히 일정한 PCB크기에 부품을 접속하기 위해 도체회로를 형성되는 정도를 실장밀도라 하는데 실장밀도를 높이기 위해서는 PCB layer수를 높이거나, 배선밀도를 높이는 방법이 있다. PCB layer의 경우 일반TV나 라디오, 계산기 등 민간생활품으로 사용하는 전자기기의 경우 10층 이하의 비교적 낮은 층수만으로도 회로형성 및 구동이 가능하다. 10층 이하의 낮은 층수의 경우 각 층마다 두께공차가 있다고 하더라도 낮은 층수이기 때문에 적층을 통한 최종 생성품 에서는 뒤틀림 및 제품의 불량이 일어날 확률이 적고 high-technology가 아닌 기판끼리의 단순 접합을 통해서도 충분히 적층을 할 수 있었다.

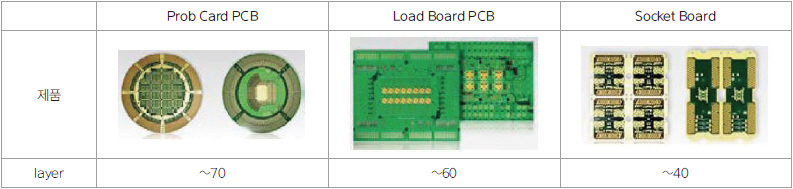

하지만 고성능, 고신뢰성이 요구되는 probe card PCB, load board PCB를 비롯한 특수 PCB의 경우 50층 이상의 초고다층을 가지기 때문에 단순 접합을 통하여서는 특수 PCB를 적층 할 수 없다. 또한 각 층마다 두께공차가 생기면 층수가 많기 때문에 공차가 쌓여 결국 뒤틀림 현상 및 불량품을 생성 할 수 있다. 표 1은 특수 PCB종류별 필요로 하는 층수를 나타내었다.

▲ 표 1. 특수 PCB 종류별 요구 Layer

고다층 적층시 내층 패터닝을 하기 위해 Cu 적층, 비아형성, 도금, 노광, 현상, 에칭 등을 매층 반복하여야 하기 때문에 적층수가 증가하면 제조비용도 층수에 비례해서 증가한다.4) 그렇기 때문에 제조시 불량이 발생하게 되면 그만큼 기업 입장에서는 손해가 매우 크기 때문에 불량률을 감소하고 재연성을 부여하기 위한 초고다층의 PCB를 제조하기 위하여 많은 연구를 하고 있다.

먼저 각층마다 두께공차를 줄이는 방법으로는 패터닝을 하기 위해 Dry film을 붙이기 전 구리 표면을 전처리(정면) 하는데 이 전처리의 방식을 바꾸는 방법이다. 정면의 방식으로는 브러쉬 정면, Pumice 정면, Jet scrub(pumice)정면, Jet scrub(Al2O3)정면, chemical clean등이 있다. 박판 PCB의 경우 과거에는 브러쉬 정면을 하였지만 화학적, 기계적 scrubbing이 동시에 일어나 구리를 많이 깎아내고 그로인하여 두께공차가 일어나는 문제점이 있기 때문에 최근에는 Jet scrub정면 및 화학적 정면을 사용하며 보통 화학적 정면을 많이 사용한다.5)

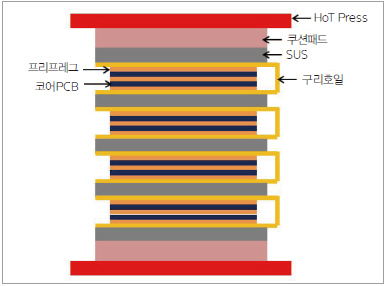

다음은 적층 공정시 뒤틀림 방지 및 쏠림 현상을 방지하고 불량률을 줄이는 연구로써 hot press를 이용하여 PCB를 적층하는데 이 때 hot press 열판 전체가 일정한 온도를 유지하여야 하며 그러지 않을 경우 프리프레그가 부분적으로 용융이 되어 한쪽방향으로 흐르게 되고 결과적으로 두께가 일정하기 못하는 불량이 발생할 수 있는데 이러한 문제점을 해결하기 위하여 초음파를 이용하여 프리프레그만 용융시킬 수 있는 주파수를 발생시켜 프리프레그를 골고루 용융시켜 적층시킬 수 있는 특허6)가 출원이 된 적이 있었으며(그림 7) 또다른 특허로써 hot press동안 다수의 기판에 온도구배가 발생하고 이는 적층 후 기판들이 스케일 편차가 증가되는 문제점이 발생하여 이를 해결하기위하여 Cu호일을 이용하여 PCB 및 쿠션패드를 감싸 온도편차를 줄여주는 특허가 등록된 적이 있다.7) 특허에 대한 모식도는 그림 8에 나타냈다.

▲ 그림 7. 초음파를 이용한 적층방법

▲ 그림 8. 구리호일을 감싸 온도차이를 줄여 적층하는 방법

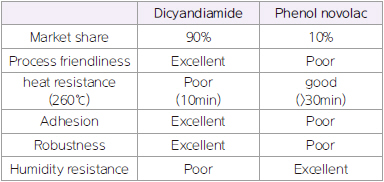

한편 프리프레그의 재료로 사용되는 Dicyandiamide와 Phenol novolac의 단점을 에폭시와 결합하여 결점을 제거하는 논문이 발표된 적도 있었다. 8) 표 2는 Dicyandia-mide와 Phenol novolac의 특성을 나타냈다.

▲ 표 2. Dicyandiamide와 Phenol novolac의 특성

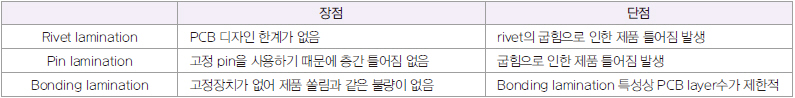

현재 사업체에서 사용하는 초다층 PCB 적층의 경우 크게 Rivet lamination, Pin lamination, Bonding lamination이 있으며 각각의 장·단점이 있다. 그렇기 때문에 PCB용도에 맞게 사용하고 있다. 아래 표 3은 Rivet lamination, Pin lamination, Bonding lamination의 대표적 장·단점을 나열했다.

▲ 표 3. 적층 종류별 장·단점

Lamination관련 내용은 다층 적층 bonding 기술 부분에서 다루기 때문에 더 이상의 내용은 생략한다.

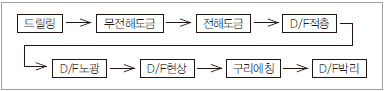

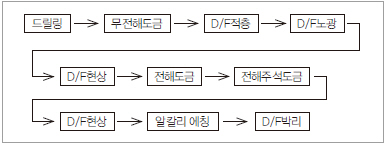

실장밀도를 높이는 방법으로 PCB layer수를 높이는 방법 외에 배선밀도를 높이는 방법도 있다. 배선밀도를 높이기 위해서는 회로 폭과 회로간 간격을 줄여 일정한 PCB기판 면적에 더욱더 많은 회로를 형성할 수 있어야 한다. 현재 사업체에서 PCB 회로 패터닝을 하는 방법으로는 dry film을 기판에 붙여 회로를 노광하고 현상 및 에칭을 통하여 구리를 깎아내서 회로를 형성하는 방법을 사용하고 있다. 이러한 dry film을 이용한 회로 패터닝은 또다시 판넬법과 패턴법으로 구분된다. 그림 9와 그림 10는 판넬법과 패턴법을 이용한 회로 패터닝 공정도 이다.

▲ 그림 9. 판넬법을 이용한 회로 패터닝 공정도

▲ 그림 10. 패턴법을 이용한 회로 패터닝 공정도

기본적으로 에칭을 통하여 회로 패터닝을 하기전 무전해도금 및 전해도금을 실시하는데 무전해도금 및 전해도금은 홀도금을 하기 위하여 실시하는 것이다. 따라서 외층의 경우 기존 CCL에 도금으로 인한 두께가 추가되며 추가된 구리의 상태로 회로 패터닝을 실시하여야 한다. 판넬법과 패턴법의 공정도를 보면 약간의 차이가 있는데 판넬법의 경우 무전해도금 후 바로 전해도금을 실시하고 dry film을 부착하여 노광 및 현상후 회로형성을 하는 반면 패턴법의 경우 무전해도금후 dry film을 노광 및 현상후에 전해도금을 실시한다.

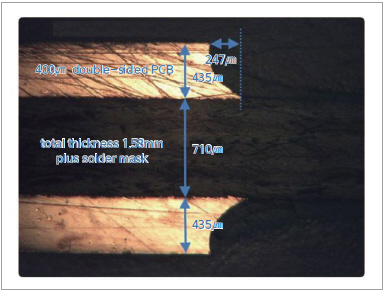

이러한 순서의 차이는 에칭공정에서 에칭을 할 때 제거해야할 구리의 두께가 달라진다. 판넬법의 경우 CCL(35μm) + 무전해도금(4μm) + 전해도금(25μm) = 64μm의 구리를 제거해야 하지만 패턴법의 경우 CCL(35μm) + 무전해도금(4μm) = 39μm의 구리만 제거하면 된다. 패턴법의 구리두께가 판넬법의 구리두께보다 약 40%적도 더 작기 때문에 그만큼 에칭하는 시간이 줄어든다. 에칭하는 시간이 줄어든다는 것은 에칭액이 회로를 형성해야 하는 구리와 접촉시간이 줄어드는 것을 의미하며 이는 회로정밀도가 향상된다는 것을 의미한다. 보통 판넬법의 경우 100 μm, 패턴법의 경우 50μm까지 회로를 구현할 수 있다.

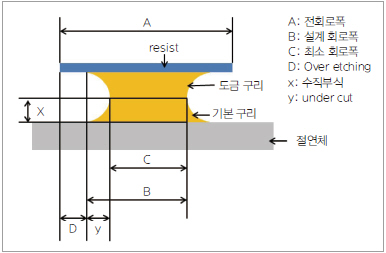

일반적으로 에칭액을 이용한 wet방법은 unnder cut이 일어난다. 그림 11은 etching 정도를 설명할 수 있는 측면도 이며 내용은 다음과 같다.5)

▲ 그림 11. etching 측면도

(1) under cut

y로 회로 가장 자리에서 측정한 최대 움푹 패인 홈의 최고 깊이 사이의 거리를 말한다. 에칭에 있어서 under cut이 적은 것이 목표로 이상적인 회로가 달성될 수 있다.

(2) etch factor

회로의 깊이에 대한 측면 에칭률을 말한다. 즉,  로 y 즉, under cut이 적다는 것은 etch factor가 커진다는 의미다.

로 y 즉, under cut이 적다는 것은 etch factor가 커진다는 의미다.

(3) etch rate

에칭의 분당 에칭률을 말하며 etch rate = μm/분으로 표기되어 에칭의 정도 지표이다.

(4) sliver

Resist의 지탱되지 않은 돌출 부분을 말하며 D에 해당된다. 즉, 이것은 곧 회로폭 감소 및 over etching과 관련된다.

그림 12는 over etching이 일어난 실제 회로를 관찰한 사진이다.

▲ 그림 12. Over etching

즉, under cut이 적다는 것은 over etching이 적다는 것이고 회로의 정밀성을 높일 수 있다는 것이다. Under cut은 구리두께와 상관관계가 있는데 에칭 하고자 하는 구리두께가 두꺼우면 그림 13과 같이 처음에는 resist와 접착이 안된 부분으로 에칭액이 침투하여 정상적으로 구리를 제거하다가 점점 진행이 되면서 회로부분의 구리를 조금씩 제거를 하여 결국 under cut이 일어나고 over etching이 되어 원하는 폭의 회로형성을 할 수 없게 된다.

▲ 그림 13. Over etching mechanism

Under cut 및 over etching은 wet방법 에서는 반드시 일어나는 현상이다. 그렇기 때문에 반도체 공정에서는 wet방법 대신 dry방법을 사용하는데 dry방법은 감압된 용기 속에서 가스 또는 이온에 의해 에칭하는 방법이며 가공 정도가 향상되는 것으로 알려져 있다.9) 대표적으로 플라즈마 에칭이 있다. dry에칭의 특징은 다음과 같다.

• 가스의 선택 및 조절이 비교적 쉽기 때문에 정확한 패턴 형성이 가능하다.

• 이방성 에칭이 가능하다.

• 에칭의 endpoint확인이 가능하다.

• 자동화 양산화에 적합하다.

• 공해나 오염 등의 문제가 없다.

PCB 패터닝 에서는 dry방법을 사용하지 않는데 dry방법은 wet방법보다 상대적으로 높은 비용이 들기 때문에 반도체 공정보다 더 넓고 많은 구리를 에칭 해야하는 PCB로써는 한계가 있다. 그렇기 때문에 PCB의 경우 wet에칭을 하면서 under cut이 적게 하기 위하여 에칭 하고자 하는 구리의 두께를 얇게 하고자 많은 노력을 하고 있다. 이론적으로 외층동박을 Ultra thin Cu foil인 3/8 oz(12.7 μm), 1/4 oz(8.5 μm), 1/8 oz(4.3 μm)을 사용하면 되지만 이러한 Ultra thin Cu foil의 제조가 어렵고, 취급 또한 어려우며 고가이다.

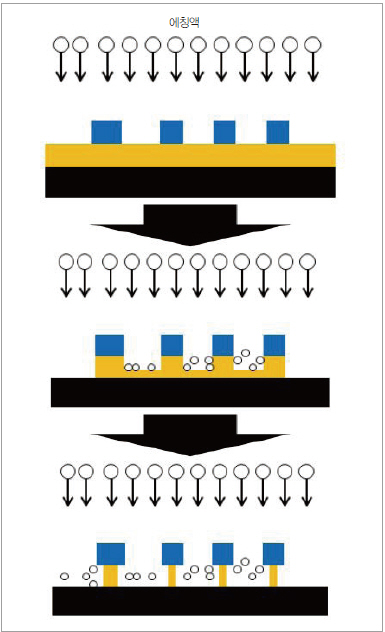

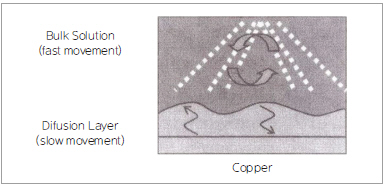

따라서 에칭공정전 half etching으로 구리를 얇게 해주고 있다. 하지만 half etching시 문제로써 그림 14와 같이 Cu의 etchant가 diffusion layer의 두께 차이로 불균일한 에칭이 된다. 이러한 불균일한 에칭의 경우 설사 정확한 회로구현을 한다고 하더라도 적층공정에서 뒤틀림 현상 및 불량을 야기 할 수 있게 된다.10) 따라서 새로운 half etching방법이나 wet방법으로 구리를 식각하는 것이 아닌 새로운 타입의 회로형성 process가 필요하다.

▲ 그림 14. etching시 etchant의 상이한 diffusion layer

기존 방법외에 미세회로를 형성하는 연구에서는 표면세척의 방법을 개선하는 연구가 있었는데 PCB를 이용한 제품 생산에 있어서, 인쇄회로기판 표면에 흡착된 먼지와 같은 이물질은 제품 불량의 주요원인이 되기 때문에 제품 생산과정에서 인쇄회로기판 표면에 흡착된 먼지와 같은 이물질을 제거하기 위하여 롤러브러쉬나 에어브러쉬 등을 이용한 세척장치를 사용하는 것이 일반적이다.

그러나 롤러브러쉬나 에어브러쉬 등을 이용해 인쇄회로기판 표면에 흡착된 먼지 등의 이물질을 제거하는 종래의 세척방식은, 세척과정에서 제품 불량의 원인이 되는 정전기가 빈번히 발생하는 문제가 있으며, 소형화 집적화 경향에 따라 회로패턴이 갈수록 미세해지는 추세에서 이물질을 효과적으로 제거하는데 한계가 있다.

더욱이, 에어브러쉬를 이용한 세척 방식의 경우, 세척을 위한 압축 공기 분사 과정에서 소음이 크게 발생하기 때문에 쾌적한 작업장 환경을 조성하기 어렵다는 단점이 있다. 이에 최근에는 순수(Ieionized water)를 이용한 습식 세척방식이 제안되었으나, 알려진 습식 장비는 한번에 작업할 수 있는 PCB 개수가 많지 않아 작업능륙이 떨어지는 단점이 있다.

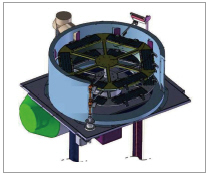

이를 해결하기 위하여 습식과 건식의 조합형 구조로서, 소형화 집적화 경향에 따라 회로패턴이 복잡해진 PCB에 대한 효율적인 세정을 도모할 수 있는 세정장비를 제공하고자하고 복층형 구성으로서 순수를 이용한 습식방식을 채택하면서도 한번에 보다 많은 양의 PCB 세정을 도모할 수 있는 세정장비를 개발한 특허가 등록 된 적이 있었다.11) 장치의 모식도는 그림 15에 나타냈다.

▲ 그림 15. 특수 설계된 세정장치의 모식도

또 다른 특허의 경우 기존 회로형성 process의 경우 2가지의 큰 문제점이 있는데 첫째로 에칭리스트에 선택적으로 노광을 하기 위해서는 포토마스크라는 회로필름을 사용하여야한다. 그러나 회로필름이 절연기판에 부착된 상태로 각종 작업이 이루어지게 되면서, 온도와 습도 등의 작업조건에 따라 회로필름의 치수에 변형이 발생할 수 있다. 이와 같은 치수의 변형에 의해 인쇄회로기판에 형성되는 회로패턴의 정밀도가 떨어지는 문제점이 발생할 수 있다. 두 번째로는 작업조건에 따른 회로필름의 치수변형과 절연기판의 치수변형을 동시에 고려하여 보호필름 및 절연체를 설계하여야 하므로, 설계과정이 복잡하다는 문제가 있다.

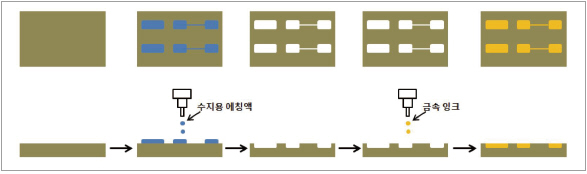

이러한 문제점들을 해결하고자 그림 16에서와 같이 포토마스크를 사용하지 않고 절연기판에 홈을 파서 그 부분에 금속잉크를 채워 넣어 미세회로를 형성하는 특허가 등록된 적이 있다. 구체적으로 설명 하자면 절연기판에 수지용 에칭액을 ink-jet 프린터를 이용하여 회로를 형성하고자 하는 곳에 도포를 하면 수지용 에칭액이 절연기판을 깎아 홈을 낸다. 홈이 형성된 부분에 다시 ink-jet printer를 이용하여 금속잉크를 채워넣어 소결을 하여 회로를 형성하는 방법이다.12)

▲ 그림 16. 수지에 홈을 파서 회로형성

하지만 이와 같은 방법에서의 문제점은 절연기판의 종류에 따라 에칭액의 선정에 주의를 요해야 하며 에칭액을 선정하였다고 하더라도 필요한 두께의 회로패턴(회로폭), 홈의 깊이 등을 조절해야 함으로 절연기판의 재질 및 에칭액의 특성, 에칭이 이루어지기 위해 방대한 데이터를 미리 확보해 놓아야 하므로 한번 공정시 오랜 연구가 필요하다는 문제점이 있다.

무엇보다 가장 큰 문제점은 이와 같이 홈을 파서 회로를 형성시 모든 기판을 해야 한다는 점인데, 전자기기의 소형화, 경량화를 위해서 배선밀도를 높이는 것이 중요하기 때문에 미세회로의 형성 또한 중요하나 모든 기판에서 미세회로를 형성하지는 않는다. 따라서 이와 같은 방법으로 회로 형성시 오히려 기존의 방법보다 제작비용의 상승 및 오랜 제작시간이 걸릴 수 있다.

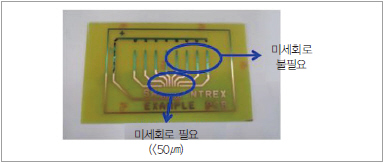

위에서도 언급된 바와 같이 PCB에서 모든 회로가 미세화 할 필요는 없다. 단지 미세회로의 형성을 해야하는 부분, 예를 들어 fan-out부분과 같이 미세회로가 필요한 부분이 있기 때문에 그 부분에서만 미세회로를 형성하면 되는 것이다. 본 과제실험을 시작하기 전 여러 문헌 자료들을 찾아 보았으나 위의 특허 외에 동박적층판(CCL)을 고온에서 열처리하여 입자를 균질화 시켜 배선의 고밀도화를 실현하는 것13)과 under etching이 일어날 부분에 합금들을 첨가하여 미세회로를 형성하는 등14) 미세회로 형성만을 위한 연구이거나 공정이 매우 복잡한 연구들이 대부분 이었다.

본 과제에서는 미세회로 형성시 복잡한 공정이 아닌 매우 간단하게 미세회로를 형성하여 제조시간을 단축 하고자 하였으며 또한 본 과제에서는 그림 17에서와 같이 필요한 부분만 미세회로를 형성하여 일반 회로의 형성은 기존 방식의 값싸고 효율적인 공정의 장점과 국소 부위를 효율적으로 미세선폭 구현 가능한 방식의 융합을 통해 각각의 장점만을 이용하여 값싸고 빠르게 구현하고자 한다.

▲ 그림 17. PCB회로 (미세회로가 필요한 Fan-out)

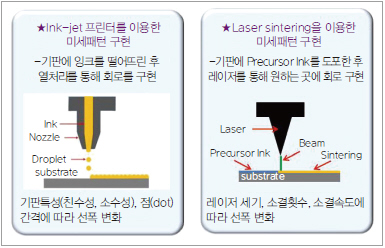

본 과제에서는 ink-jet 프린터를 이용한 미세패턴 형성 공정과 laser소결을 이용한 미세 패턴 형성을 하였다. 세부 모식도는 그림 18에 나타내었다.

▲ 그림 18. Ink-jet프린팅 공정과 laser 소결공정 모식도

Ink-jet 프린팅 공정과 laser 소결 공정을 이용하여 50 μm이하의 미세 선폭의 구현이 가능한지 확인하였고 일반 wet방식과 결합 여부에 대하여 알아보았다. 또한 미세회로 구현시 공정이 간단하기 때문에 실제 사업체에서 적용 가능한지에 대해 알아보았다.

한국생산기술연구원